- 您现在的位置:买卖IC网 > PDF目录16427 > EVAL-ADAU1442EBZ (Analog Devices Inc)BOARD EVAL FOR ADAU1442 PDF资料下载

参数资料

| 型号: | EVAL-ADAU1442EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 58/93页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADAU1442 |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 主要目的: | 音频,音频处理 |

| 嵌入式: | 是,DSP |

| 已用 IC / 零件: | ADAU1442 |

| 主要属性: | 单芯片多通道 28/56 位音频 DSP |

| 次要属性: | I²C & SPI 接口 |

| 已供物品: | 电路板,线缆,说明文档,GPIO 子板,电源 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

ADAU1442/ADAU1445/ADAU1446

Data Sheet

Rev. D | Page 60 of 92

DSP CORE

The DSP core performs calculations on audio data as specified

by the instruction codes stored in program RAM. Because

SigmaStudio generates the instructions, it is not necessary to

have a detailed knowledge of the DSP core to use the SigmaDSP,

but a brief description is provided in this section.

Architecture

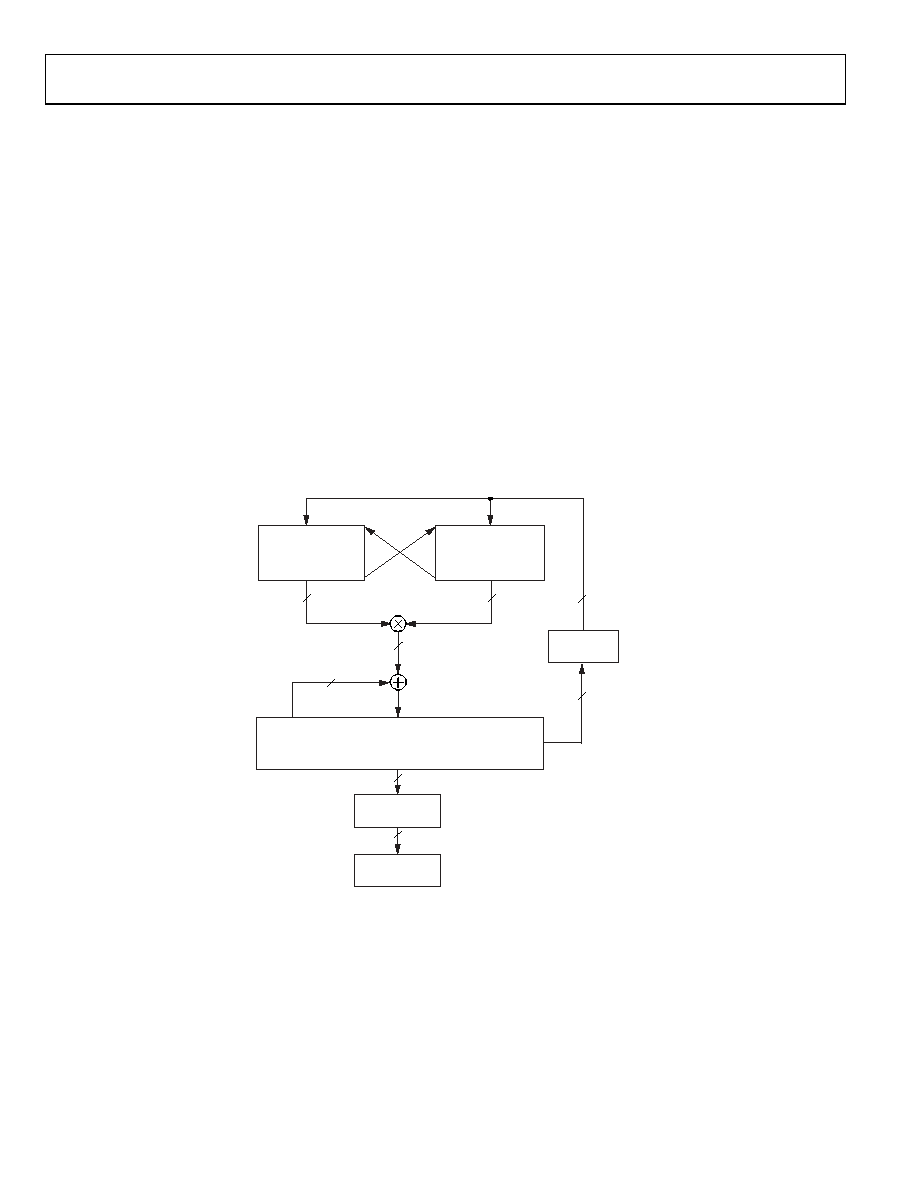

The core consists of a simple 28-/56-bit multiply-accumulate

unit (MAC) with two sources: a data source and a coefficient

source. The data source can come from the data RAM, a ROM

table of commonly used constant values, or the audio inputs to

the core. The coefficient source can come from the parameter

RAM, a ROM table of commonly used constant values. The

two sources are multiplied in a 28-bit fixed-point multiplier,

and then the signal is input to the 56-bit adder; the result is

usually stored in one of three 56-bit accumulator registers.

The accumulators can be output from the core (in 28-bit

format) or can optionally be written back into the data or

parameter RAMs.

Features

The SigmaDSP core is designed specifically for audio processing

and, therefore, includes several features intended for maximizing

efficiency. These include hardware decibel conversion and audio-

specific ROM constants.

Signal Processing

provide all signal processing functions commonly used in stereo

or multichannel playback systems. The signal processing flow is

designed using SigmaStudio software from Analog Devices. This

software allows graphical entry and real-time control of all signal

processing functions.

Many of the signal processing functions are coded using full,

56-bit, double-precision arithmetic. The serial port input and

output word lengths are 24 bits, but four extra headroom bits

are used in the processor to allow internal gains of up to 24 dB

without clipping. Additional gains can be achieved by initially

scaling down the input signal in the DSP signal flow.

COEFFICIENT SOURCE

(PARAMETER RAM,

ROM CONSTANTS, ...)

DATA OPERATIONS

(ACCUMULATORS (3), dB CONVERSION,

BIT OPERATORS, BIT SHIFTER, ...)

DATA SOURCE

(DATA RAM,

ROM CONSTANTS,

INPUTS, ...)

OUTPUTS

TRUNCATOR

56

28

56

07696-

052

Figure 51. Simplified Core Architecture

相关PDF资料 |

PDF描述 |

|---|---|

| A3AAH-4036G | IDC CABLE - ASC40H/AE40G/ASC40H |

| AMIS30622C6227RG | IC MOTOR DVR MICROSTP I2C 20SOIC |

| A1CXB-3036M | IDC CABLE- AKC30B/AE30M/X |

| VE-214-EX | CONVERTER MOD DC/DC 48V 75W |

| GCC10DRYH-S734 | CONN EDGECARD 20POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAU1446EBZ | 功能描述:BOARD EVAL FOR ADAU1446 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:SigmaDSP® 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAU1590EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

| EVAL-ADAU1592EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For ADAU1592 制造商:Analog Devices 功能描述:EVAL BOARD - Boxed Product (Development Kits) |

| EVAL-ADAU1701EB | 制造商:Analog Devices 功能描述:EVAL BOARD FOR SIGMADSP AUDIO PROCESSOR - Bulk |

| EVAL-ADAU1701EBZ | 制造商:Analog Devices 功能描述:EVAL BOARD - Bulk |

发布紧急采购,3分钟左右您将得到回复。