- 您现在的位置:买卖IC网 > PDF目录16440 > EVAL-ADAV801EBZ (Analog Devices Inc)BOARD EVALUATION FOR ADAV801 PDF资料下载

参数资料

| 型号: | EVAL-ADAV801EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/60页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR ADAV801 |

| 标准包装: | 1 |

| 主要目的: | 接口,模拟前端(AFE) |

| 已用 IC / 零件: | ADAV801 |

| 已供物品: | 板 |

| 相关产品: | ADAV801ASTZ-ND - IC CODEC AUDIO R-DVD 3.3V 64LQFP ADAV801ASTZ-REEL-ND - IC CODEC AUDIO R-DVD 3.3V 64LQFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

ADAV801

Rev. A | Page 30 of 60

INTERFACE CONTROL

The ADAV801 has a dedicated control port to allow access to

the internal registers of the ADAV801. Each of the internal

registers is eight bits wide. Where bits are described as reserved

(RES), these bits should be programmed as zero.

SPI INTERFACE

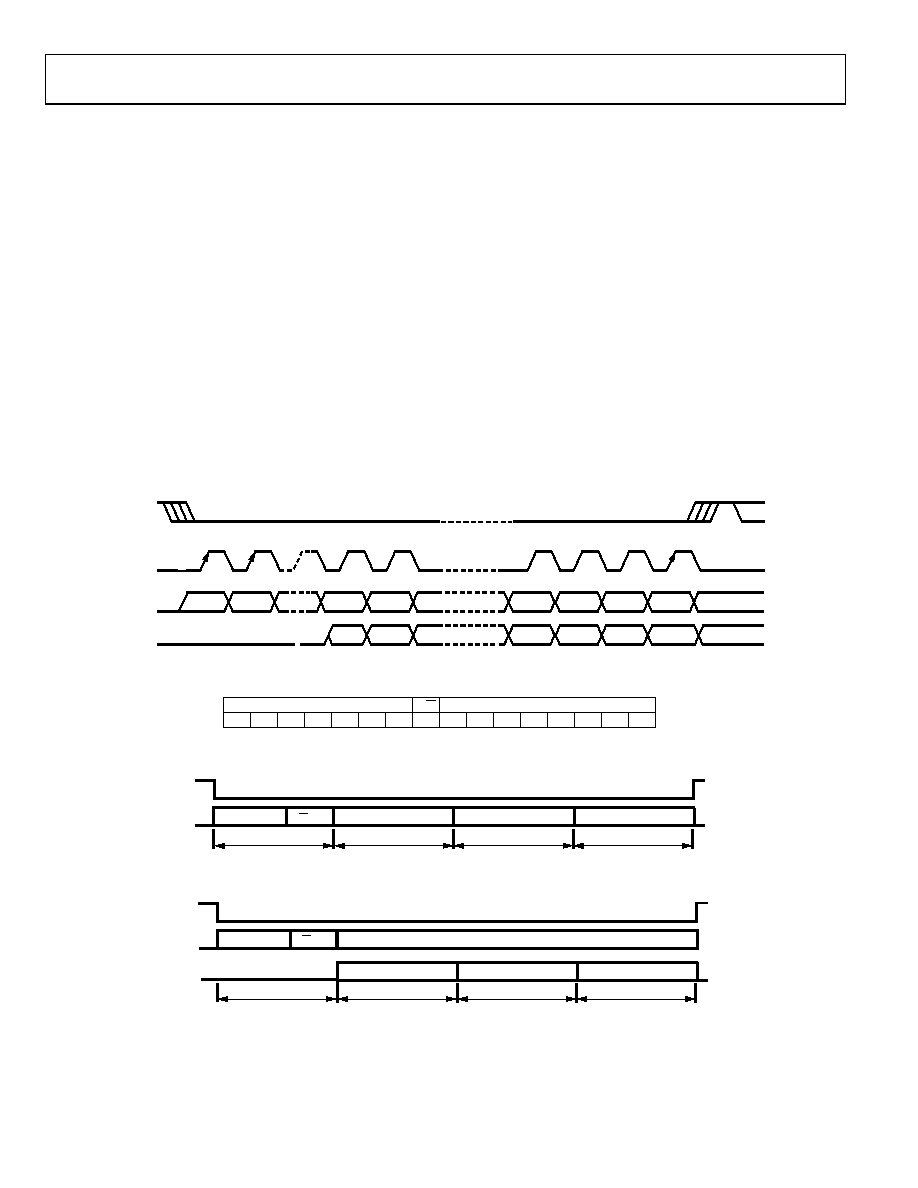

Control of the ADAV801 is via an SPI-compatible serial port.

The SPI control port is a 4-wire serial control port with one

cycle of data transfer consisting of 16 bits. Figure 53 shows the

format of an SPI write/read of the ADAV801. The transfer of

data is initiated on the falling edge of CLATCH. The data

presented on the first seven CCLKs represents the register

address read/write bit. If this bit is low, the following eight bits

of data are loaded to the register address provided. If this bit is

high, a read operation is indicated. The contents of the register

address are clocked out on the COUT pin on the following eight

CCLKs. For a read operation, the data bits after the read/write

bits are ignored.

BLOCK READS AND WRITES

The ADAV801 provides the user with the ability to write to or

read from a block of registers in one continuous operation. In

SPI mode, the CLATCH line should be held low for longer than

the 16 CCLK periods to use the block read/write mode. For a

write operation, once the LSB has been clocked into the

ADAV801 on the 16th CCLK, the register address as specified

by the first seven bits of the write operation is incremented and

the next eight bits are clocked into the next register address.

The read operation is similar. Once the LSB of a read register

operation has been clocked out, the register address is

incremented and the data from the next register is clocked out

timing diagrams for the block write and read operations.

CLATCH

CCLK

CIN

COUT

D0

D8

D0

D15

D14

D9

D8

D9

0

45

77

-0

33

Figure 53. SPI Serial Port Timing Diagram

14

13

12

11

10

9

876543210

R/W

15

ADDRESS [6:0]

DATA [7:0]

04

57

7-

03

6

Figure 54. SPI Control Word Format

0

45

77-

0

34

REGISTER

REGISTER DATA

REGISTER + 1 DATA

REGISTER + 2 DATA

R/W = 0

8 BITS

CLATCH

CIN

Figure 55. SPI Block Write Operation

0

45

77

-03

5

REGISTER

REGISTER DATA

REGISTER + 1 DATA

REGISTER + 2 DATA

R/W = 1

8 BITS

CLATCH

CIN

DON’T CARE

COUT

Figure 56. SPI Block Read Operation

相关PDF资料 |

PDF描述 |

|---|---|

| H1WXH-2636M | IDC CABLE - HPL26H/AE26M/X |

| VE-211-EX | CONVERTER MOD DC/DC 12V 75W |

| EVAL-ADE5169EBZ-2 | BOARD EVALUATION FOR AD5169 |

| VE-J1M-EX | CONVERTER MINIMOD DC/DC 10V 75W |

| VE-21M-EX | CONVERTER MOD DC/DC 10V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADAV803EBZ | 功能描述:BOARD EVALUATION FOR ADAV803 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADCMP551BRQ | 制造商:Analog Devices 功能描述:EVALUATION BOARD-HIGH SPEED COMPARATOR - Bulk |

| EVAL-ADCMP551BRQZ | 功能描述:BOARD EVALUATION ADCMP551BRQZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| EVAL-ADCMP552BRQ | 制造商:AD 制造商全称:Analog Devices 功能描述:Single-Supply, High Speed PECL/LVPECL Comparators |

| EVAL-ADCMP552BRQZ | 功能描述:BOARD EVALUATION ADCMP552BRQZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。