- 您现在的位置:买卖IC网 > PDF目录385376 > HFA3860BIV (HARRIS SEMICONDUCTOR) 3.3V 288-mc CPLD PDF资料下载

参数资料

| 型号: | HFA3860BIV |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | 3.3V 288-mc CPLD |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件页数: | 14/40页 |

| 文件大小: | 272K |

| 代理商: | HFA3860BIV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

4-14

Service Field (8 Bits) -

This field has one bit that is used to

supplement the length field and the rest are currently

unassigned and can be utilized as required by the user. Set

them to 0’s for compliance with IEEE 802.11. The MSB of

this field is used by the Media Access controller (MAC) to

indicate the correct choice when the length field is

ambiguous.

Length Field (16 Bits) -

This field indicates the number of

microseconds it will take to transmit the payload data

(MPDU). The external controller will check the length field in

determining when it needs to de-assert RX_PE.

CCITT - CRC 16 Field (16 Bits) -

This field includes the

16-bit CCITT - CRC 16 calculation of the three header fields.

This value is compared with the CCITT - CRC 16 code

calculated at the receiver. The HFA3860B receiver will

indicate a CCITT - CRC 16 error via CR24 bit 2 and will

lower MD_RDY if there is an error.

The CRC or cyclic Redundancy Check is a CCITT CRC-16

FCS (frame check sequence). It is the ones compliment of

the remainder generated by the modulo 2 division of the

protected bits by the polynomial:

x

16

+ x

12

+ x

5

+ 1

The protected bits are processed in transmit order. All CRC

calculations are made prior to data scrambling. A shift

register with two taps is used for the calculation. It is preset

to all ones and then the protected fields are shifted through

the register. The output is then complemented and the

residual shifted out MSB first.

The following Configuration Registers (CR) are used to

program the preamble/header functions, more programming

details about these registers can be found in the Control

Registers section of this document:

CR 6 -

Defines the preamble length minus the SFD in

symbols. The 802.11 protocol requires a setting of

128d = 80h.

CR 15 -

Defines the length of time that the demodulator

searches for the SFD before returning to acquisition.

CR 16 -

The contents of this register define DBPSK

modulation. If CR 20 bits 1 and 0 are set to indicate DBPSK

modulation then the contents of this register are transmitted in

the signal field of the header.

CR 17 -

The contents of this register define DQPSK

modulation. If CR 20 bits 1 and 0 are set to indicate DQPSK

modulation then the contents of this register are transmitted in

the signal field of the header.

CR 18 -

The contents of this register define BMBOK

modulation. If CR 20 bits 1 and 0 are set to indicate BMBOK

modulation then the contents of this register are transmitted in

the signal field of the header.

CR 19 -

The contents of this register define QMBOK

modulation. If CR 20 bits 1 and 0 are set to indicate QMBOK

modulation then the contents of this register are transmitted in

the signal field of the header.

CR 20 -

The last two bits of the register indicate what

modulation is to be used for the data portion of the packet.

CR 21 -

The value to be used in the Service field.

CR 22, 23 -

Defines the value of the transmit data length field.

This value includes all symbols following the last header field

symbol and is in microseconds required to transmit the data at

the chosen data rate.

The packet consists of the preamble, header and MAC

protocol data unit (MPDU). The data is transmitted exactly

as received from the control processor. Some dummy bits

will be appended to the end of the packet to insure an

orderly shutdown of the transmitter. This prevents spectrum

splatter. At the end of a packet plus 3 symbols, the external

controller is expected to de-assert the TX_PE line to shut the

transmitter down.

Scrambler and Data Encoder Description

The modulator has a data scrambler that implements the

scrambling algorithm specified in the IEEE 802.11 standard.

This scrambler is used for the preamble, header, and data in

all modes. The data scrambler is a self synchronizing circuit.

It consist of a 7-bit shift register with feedback from specified

taps of the register, as programmed through configuration

register CR 7. Both transmitter and receiver use the same

scrambling algorithm. The scrambler can be disabled by

setting the taps to 0.

Be advised that the IEEE 802.11 compliant scrambler in the

HFA3860B has the property that it can lock up (stop

scrambling) on random data followed by repetitive bit

patterns. The probability of this happening is 1/128. The

patterns that have been identified are all zeros, all ones,

repeated 10s, repeated 1100s, and repeated 111000s. Any

break in the repetitive pattern will restart the scrambler. If an

all zeros pattern following random data causes the scrambler

to lock up and this state lasts for more than 200

microseconds in the BMBOK and QMBOK data modes, the

demodulator may lose carrier tracking and corrupt the

packet. This is caused by a buildup of a DC bias in the AC

coupling between the HFA3724 and the HFA3860B.

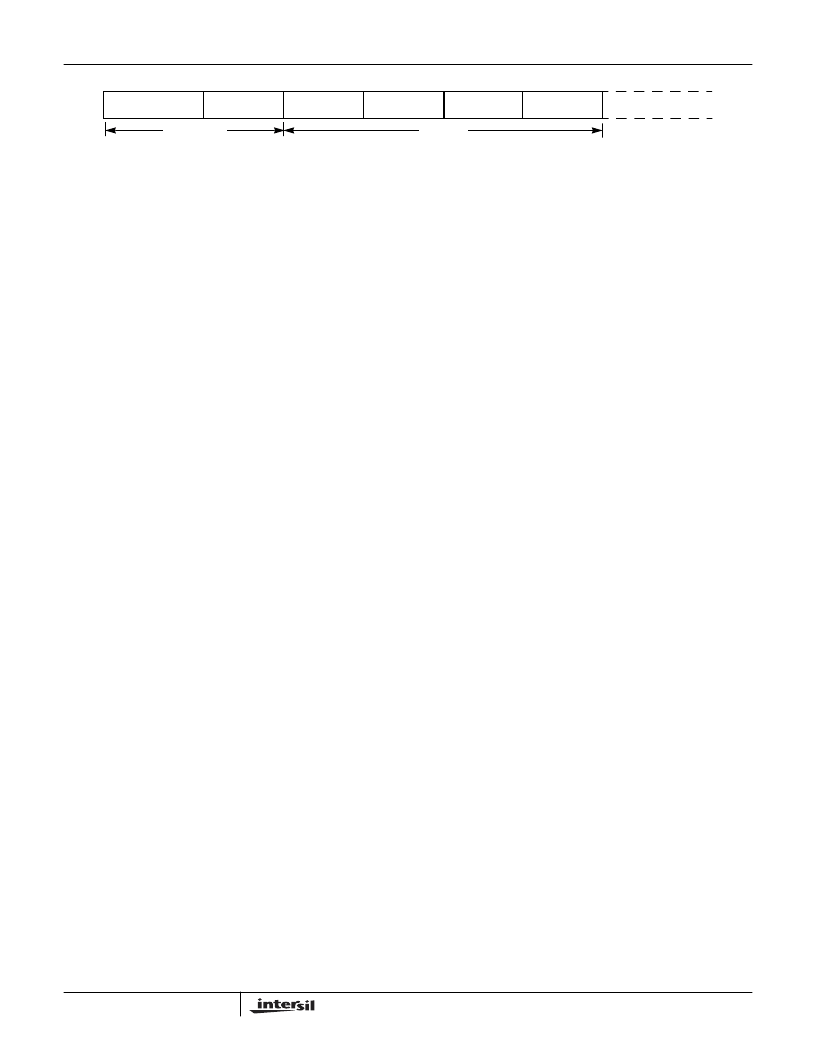

PREAMBLE (SYNC)

128 BITS

SFD

16 BITS

SIGNAL FIELD

8 BITS

SERVICE FIELD

8 BITS

LENGTH FIELD

16 BITS

CRC16

16 BITS

HEADER

PREAMBLE

FIGURE 9. 802.11 PREAMBLE/HEADER

HFA3860B

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3860BIV96 | nullDirect Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925IA | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA3925IA96 | null2.4GHz - 2.5GHz 250mW Power Amplifier |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3860BIV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860BIV96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3860IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。