- 您现在的位置:买卖IC网 > PDF目录385376 > HFA3860BIV (HARRIS SEMICONDUCTOR) 3.3V 288-mc CPLD PDF资料下载

参数资料

| 型号: | HFA3860BIV |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | 3.3V 288-mc CPLD |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件页数: | 15/40页 |

| 文件大小: | 272K |

| 代理商: | HFA3860BIV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

4-15

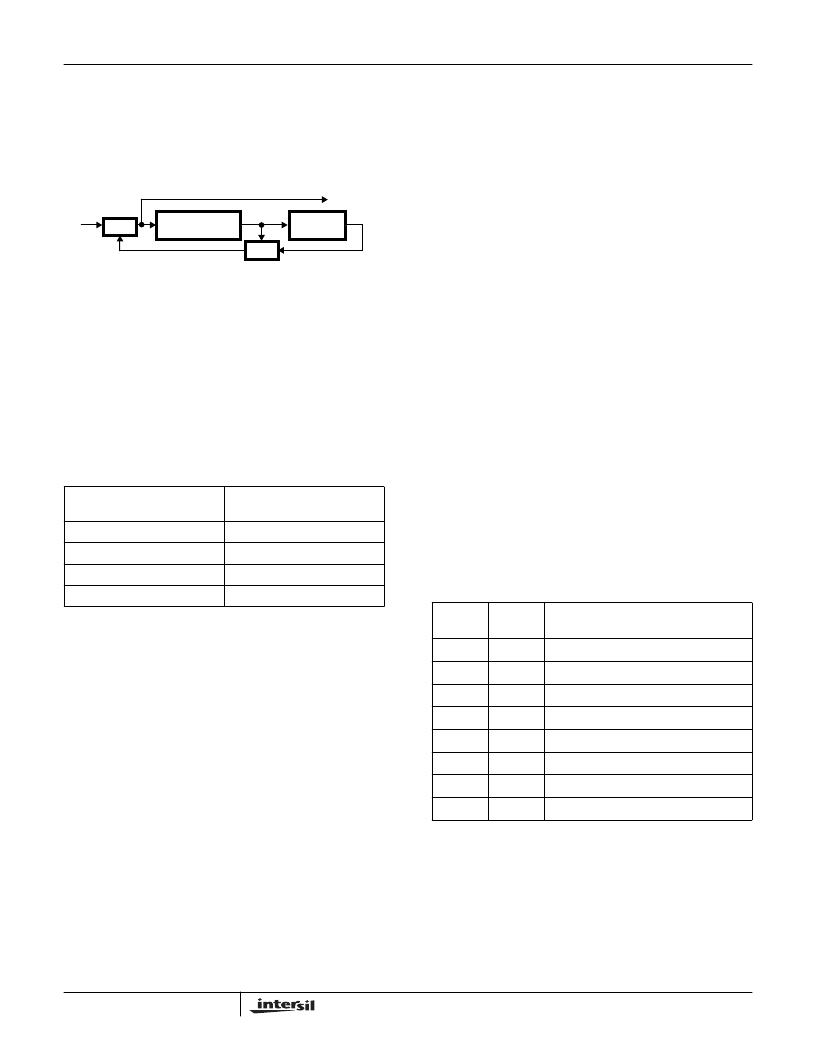

Scrambling is done by a polynomial division using a

prescribed polynomial as shown in Figure 10. A shift register

holds the last quotient and the output is the exclusive-or of

the data and the sum of taps in the shift register. The taps

are programmable. The transmit scrambler seed is Hex 6C

and the taps are set with CR7.

For the 1MBPS DBPSK data rates and for the header in all

rates, the data coder implements the desired DBPSK coding by

differential encoding the serial data from the scrambler and

driving both the I and Q output channels together. For the

2MBPS DQPSK data rate, the data coder implements the

desired coding as shown in the DQPSK Data Encoder table.

This coding scheme results from differential coding of dibits (2

bits). Vector rotation is counterclockwise although bits 5 and 6

of configuration register CR2 can be used to reverse the

rotation sense of the TX or RX signal if needed.

For data modulation in the MBOK modes, the data is formed

into nibbles (4 bits). For Binary MBOK modulation

(5.5MBPS) one nibble is used per symbol and for

Quaternary MBOK (11Mbps), two are used. The data is not

differentially encoded, just scrambled, in these modes. For

the 5.5Mbps CCK modulation, the data is formed into

nibbles and one is used for each symbol. The symbols are

differentially encoded and all odd symbols are given an

additional 180 degree rotation.

Spread Spectrum Modulator Description

The modulator is designed to generate DBPSK, DQPSK,

BMBOK, QMBOK, and CCK spread spectrum signals. The

modulator is capable of automatically switching its rate

where the preamble and header are DBPSK modulated, and

the data is modulated differently. The modulator can support

date rates of 1, 2, 5.5 and 11Mbps. The programming details

to set up the modulator are given at the introductory

paragraph of this section. The HFA3860B utilizes

Quadraphase (I/Q) modulation at baseband for all

modulation modes.

In the 1MBPS DBPSK mode, the I and Q Channels are

connected together and driven with the output of the

scrambler and differential encoder. The I and Q Channels

are then both multiplied with the 11-bit Barker word at the

spread rate. The I and Q signals go to the Quadrature

upconverter (HFA3724) to be modulated onto a carrier.

Thus, the spreading and data modulation are BPSK

modulated onto the carrier.

For the 2MBPS DQPSK mode, the serial data is formed into

dibits or bit pairs in the differential encoder as detailed

above. One of the bits in a dibit goes to the I Channel and

the other to the Q Channel. The I and Q Channels are then

both multiplied with the 11-bit Barker word at the spread

rate. This forms QPSK modulation at the symbol rate with

BPSK modulation at the spread rate.

For the 5.5MBPS Binary M-Ary Bi-Orthogonal Keying

(BMBOK) mode, the output of the scrambler is partitioned into

nibbles of sign-magnitude (4 bits LSB first). The magnitude

bits are used to select 1 of 8 eight bit modified Walsh

functions. The Walsh functions are modified by adding hex 03

to all members of a Walsh function set to insure that there is

no all 0 member as shown in Table 9. The selected function is

then XOR’ed with the sign bit and connected to both I and Q

outputs. The modified Walsh functions are clocked out at the

spread rate (nominally 11 MCPS). The symbol rate is 1/8th of

this rate. The Differential Encoder output of the last bit of the

header CRC is the phase reference for the high rate data.

This reference is XOR’ed with the I and Q data before the

output. This allows the demodulator to compensate for phase

ambiguity without differential encoding the high rate data.

For the 11MBPS QMBOK mode, the output of the scrambler

is partitioned into two nibbles. Each nibble is used as above

to select a modified Walsh function and set its sign. The first

of these modified Walsh spreading functions goes to the Q

Channel and the second to the I Channel. They are then

both XOR’ed with the phase reference developed from the

last bit of the header CRC from the differential encoder.

TABLE 8. DQPSK DATA ENCODER

PHASE SHIFT

DIBIT PATTERN (D0, D1)

D0 IS FIRST IN TIME

0

00

+90

01

+180

11

-90

10

FIGURE 10. SCRAMBLING PROCESS

Z

-1

Z

-2

Z

-3

Z

-4

Z

-5

Z

-6

Z

-7

XOR

SERIAL DATA

IN

XOR

SERIAL

DATA OUT

TABLE 9. MODIFIED WALSH FUNCTIONS

MAG

mWAL

DATA PATTERN

LSB.......MSB

0

03

11000000

1

0C

00110000

2

30

00001100

3

3F

11111100

4

56

01101010

5

59

10011010

6

65

10100110

7

6A

01010110

HFA3860B

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3860BIV96 | nullDirect Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925IA | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA3925IA96 | null2.4GHz - 2.5GHz 250mW Power Amplifier |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3860BIV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860BIV96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HFA3860IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。