参数资料

| 型号: | HMP8156ACNZ |

| 厂商: | Intersil |

| 文件页数: | 9/34页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO ENCODER NTSC/PAL 64MQFP |

| 标准包装: | 84 |

| 类型: | NTSC/PAL 编码器 |

| 应用: | 多媒体,视频编辑 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-BQFP |

| 供应商设备封装: | 64-MQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

17

FN4343.5

August 20, 2009

The host processor may still read from and write to the

internal control registers.

Host Interfaces

Reset

The HMP8154/HMP8156A resets to its default operating

mode on power up, when the reset pin is asserted for at

least four CLK cycles, or when the software reset bit of the

host control register is set. During the reset cycle, the

encoder returns its internal registers to their reset state and

deactivates the I2C interface.

I2C Interface

The HMP8154/HMP8156A provides a standard I2C interface

and supports fast-mode (up to 400 Kbps) transfers. The

device acts as a slave for receiving and transmitting data

only. It will not respond to general calls or initiate a transfer.

The encoder’s slave address is either 0100 000xB when the

SA input pin is low or 0100 001xB when it is high. (The ‘x’ bit

in the address is the I2C read flag.)

The I2C interface consists of the SDA and SCL pins. When

the interface is not active, SCL and SDA must be pulled high

using external 4-6k

Ω pull-up resistors. The I2C clock and

During I2C write cycles, the first data byte after the slave

address specifies the sub address, and is written into the

address register. Only the seven LSBs of the subaddress

are used; the MSB is ignored. Any remaining data bytes in

the I2C write cycle are written to the control registers,

beginning with the register specified by the address register.

The 7-bit address register is incremented after each data

byte in the I2C write cycle. Data written to reserved bits

within registers or reserved registers is ignored.

During I2C read cycles, data from the control register

specified by the address register is output. The address

register is incremented after each data byte in the I2C read

cycle. Reserved bits within registers return a value of “0”.

Reserved registers return a value of 00H.

The HMP8154/HMP8156A’s operating modes are

determined by the contents of its internal registers which are

accessed via the I2C interface. All internal registers may be

written or read by the host processor at any time. However,

some of the bits and words are read only or reserved and

data written to these bits is ignored.

Table 10 lists the HMP8154/HMP8156A’s internal registers.

Their bit descriptions are listed in Tables 11-30.

TABLE 10. CONTROL REGISTER NAMES

SUB ADDRESS

(HEX)

CONTROL REGISTER

RESET

CONDITION

00

01

02

03

04

05

06

07-0E

0F

10

11

12

13

14-1F

20

21

22

23

24

25

26

27

28-2F

30-7F

Product ID

Output Format

Input Format

Video Processing

Timing I/O 1

Timing I/O 2

Aux Data Enable

Reserved

Host Control

Closed Caption_21A

Closed Caption_21B

Closed Caption_284A

Closed Caption_284B

Reserved

Start H_Blank Low

Start H_Blank High

End H_Blank

Start V_Blank Low

Start V_Blank High

End V_Blank

Field Control 1

Field Control 2

Reserved

Test and Unused

54H

00H

06H

A0H

00H

-

0CH

80H

-

4AH

03H

7AH

03H

01H

13H

80H

00H

-

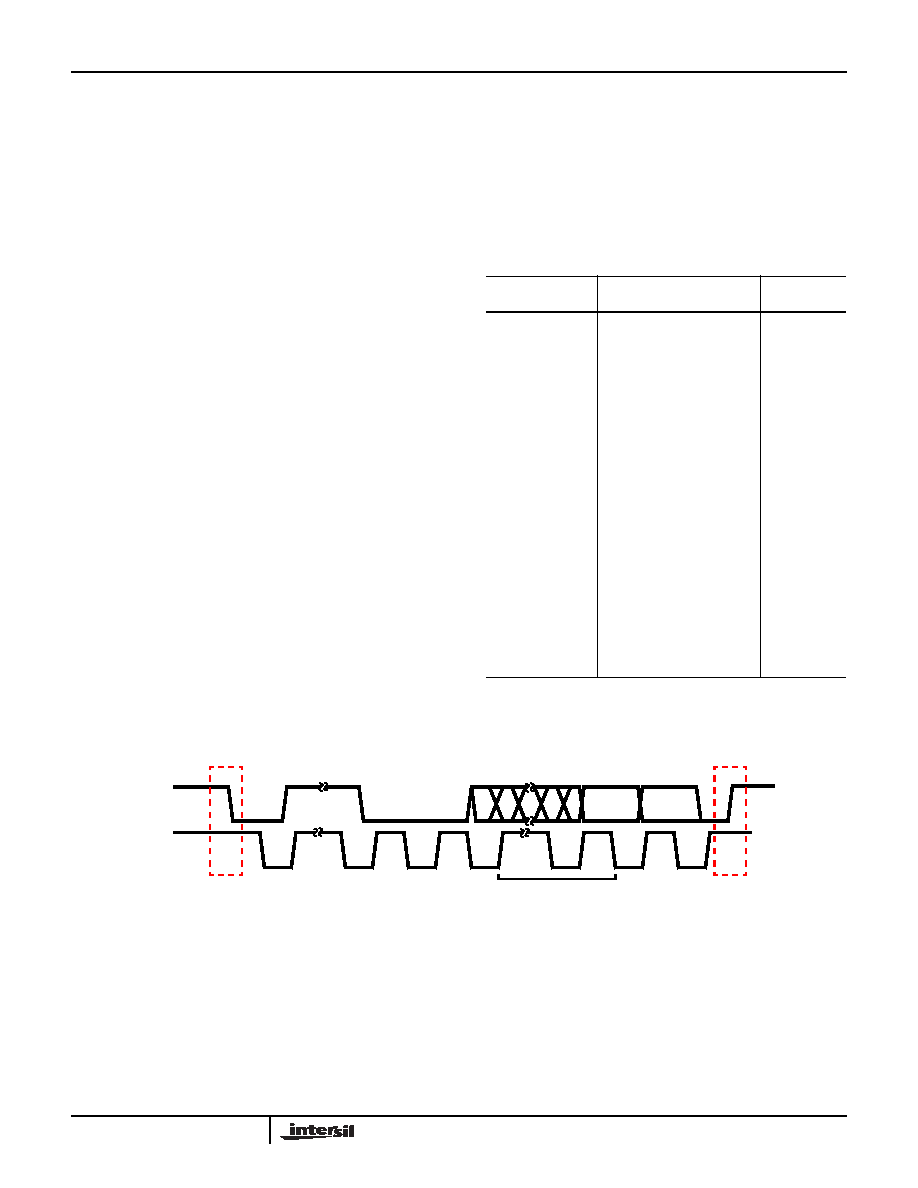

FIGURE 20. I2C SERIAL TIMING FLOW

SDA

SCL

START

CONDITION

S

1-7

ADDRESS

8

R/W

9

ACK

1-7

DATA

89

ACK

STOP

CONDITION

P

HMP8154, HMP8156A

相关PDF资料 |

PDF描述 |

|---|---|

| HSP45102SC-40Z | IC OSC NCO 40MHZ 28-SOIC |

| HSP45106JC-33Z | IC OSC NCO 33MHZ 84-PLCC |

| HSP45116AVC-52Z | IC OSC NCO 52MHZ 160-MQFP |

| ICL7109EPL+ | IC ADC 12BIT 3-ST 40-DIP |

| ICM7217AIPI | IC OSC UP/DWN CNTR 2MHZ 28-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMP8156CN | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8156EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Encoders |

| HMP8156EVAL2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HMP8170 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8170_03 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

发布紧急采购,3分钟左右您将得到回复。