参数资料

| 型号: | HSP43124SC-45Z |

| 厂商: | Intersil |

| 文件页数: | 14/18页 |

| 文件大小: | 0K |

| 描述: | IC I/O FILTER SER 24BIT 28-SOIC |

| 标准包装: | 26 |

| 滤波器类型: | 串行输入/输出 |

| 滤波器数: | 6 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

5

Writing Coefficients

The HSP43124 provides a register bank to store filter

coefficients for configurations which use the programmable

filter. The register bank consists of 128 thirty-two-bit

registers. Each register is loaded by 4 one byte writes to the

bidirectional interface used for loading the configuration

registers. The coefficients are loaded in order from least

significant byte (LSB) to most significant byte (MSB).

The coefficient registers are loaded by first setting the

coefficient read enable bit to “0” (bit 4 of the Filter

Configuration Register). Next, coefficients are loaded by

setting the A2-0 address to 010 (binary) and writing one byte

at a time as shown in Figure 3. The down loaded bytes are

stored in a holding register until the 4th write cycle. On

completion of the fourth write cycle, the contents of the

holding register are loaded into the Coefficient RAM, and the

write pointer is incremented to the next register. If the user

attempts to write more than 128 coefficients, the pointer

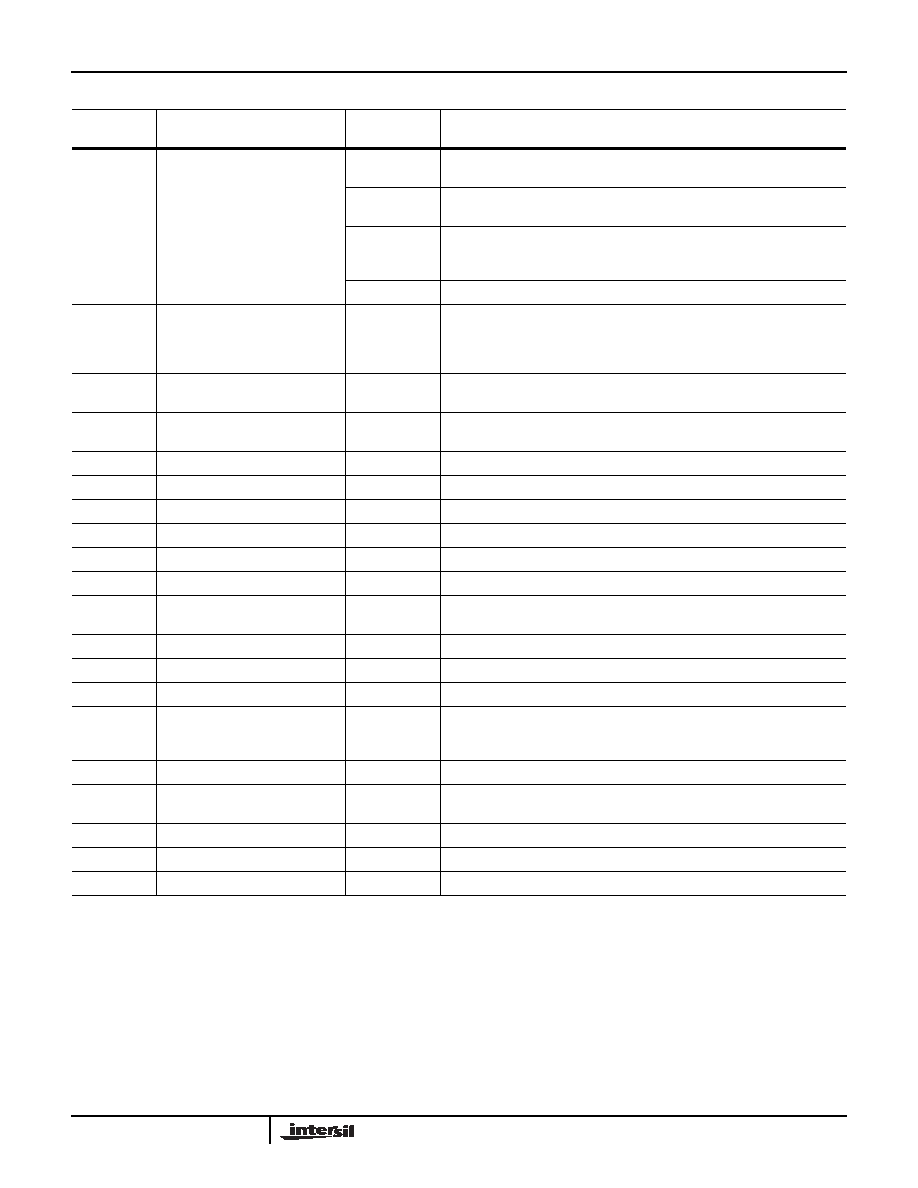

TABLE 1. CONFIGURATION CONTROL REGISTER FUNCTIONAL DESCRIPTION

ADDRESS

REGISTER DESCRIPTION

BIT

POSITIONS

BIT FUNCTION

000

Filter Configuration

2-0

Specifies the number of halfbands to use. Number ranges from 0 to 5. Other

values are invalid.

3

Filter Enable bit. 1 = Enable. 0 = Minimum filter bypass (either the FIR or

HBF must be enabled to get an output).

4

Coefficient read enable. When set to 1, enables reading and disables writing

of coefficient RAM. NOTE: This bit must be set to 0 prior to writing the

Coefficient RAM.

7-5

FIR Decimation Rate. Range is 1-8 (8 = 000).

001

Programmable FIR Filter Length

7-0

Number of Taps in the Programmable FIR Filter. For even or odd symmetric

filters, values range from 4- 256, 1 to 3 are invalid, and 0000000 = 256. For

asymmetric filters, the value loaded in this register must be two times the ac-

tual number of coefficients.

010

Coefficient RAM Access

7-0

Coefficient RAM is loaded by multiple writes to this address. (See Writing

Coefficients section for additional details.)

011

Input Format

4-0

Number of bits in input data word, from 8 (01000) to 24 (11000). Values out-

side the range of 8 - 24 are invalid.

5

Number System. 0 = Two’s Complement, 1 = Offset Binary.

6

Serial Format. 1 = MSB First, 0 = LSB First.

7Unused

100

Output Timing

4-0

Number of FCLKS per CLKOUT. Range 1 to 32. (00000 = 32 FCLKS)

5

1 = MSB First, 0 = LSB First.

6-7

Unused

101

Output Format

4-0

Number of bits in output data word, from 8 to 32. A value of 32 is represented

by 00000, and values from 1 to 7 are invalid.

5

Round Select. 1 = Round to Selected Number of Bits, 0 = Truncate.

6

Number System. 0 = Two’s Complement, 1 = Offset Binary.

7

Gain Correction. 1 = Apply scale factor of 2 to data. 0 = No Scaling.

110

Filter Symmetry

1-0

00 = Even Symmetric FIR Coefficients

01 = Non-Symmetric Coefficients

10 = Odd Symmetric FIR

7-2

Reserved: Must be 0.

111

Mix Factor Format

4-0

Number of bits in mix factor, from 8 (01000) to 24 (11000). Values outside

the range of 8 - 24 are invalid.

5

Serial Format. 1 = MSB First, 0 = LSB First.

6

Mix Factor Select. 1 = Serial Input, 0 = Weaver modulator look-up-table.

7

Unused

HSP43124

相关PDF资料 |

PDF描述 |

|---|---|

| HSP43168JC-33Z | IC FIR FILTER DUAL 84-PLCC |

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA188ES-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HSP43124SI40 | 制造商:Harris Corporation 功能描述: |

| HSP43124SI-40 | 制造商:Rochester Electronics LLC 功能描述:SERIAL FILTER,28 SOIC,40MHHZ,IND - Bulk |

| HSP43168 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168/883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168_07 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

发布紧急采购,3分钟左右您将得到回复。