参数资料

| 型号: | HSP43124SC-45Z |

| 厂商: | Intersil |

| 文件页数: | 17/18页 |

| 文件大小: | 0K |

| 描述: | IC I/O FILTER SER 24BIT 28-SOIC |

| 标准包装: | 26 |

| 滤波器类型: | 串行输入/输出 |

| 滤波器数: | 6 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

8

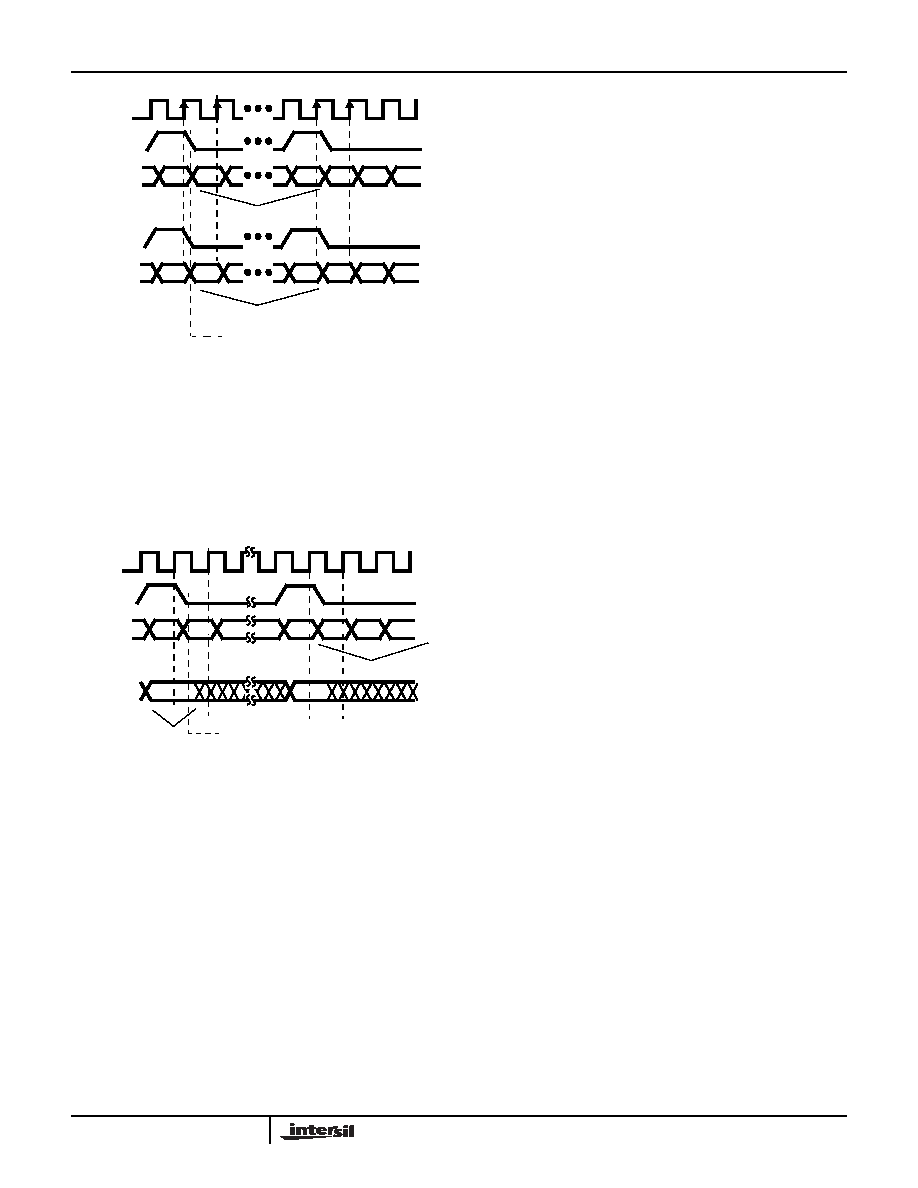

NOTE: Figure 8 shows the loading of a data sample, X0, such

that it will be multiplied by a mix factor designated by M0. For

mix factor bit widths which are less than the input bit width,

SYNCMX may be asserted before SYNCIN if desired.

If the mix factor is generated by the Weaver Modulator ROM,

the mix factor must be specified on MXIN and SYNCMX one

SYNCIN before that which precedes the target data word

(see Figure 9).

Filter Compute Engine

The Filter Compute Engine centers around a multiply

accumulator which is used to perform the sum-of-products

required for a variety of filtering configurations. These

configurations include a cascade of up to 5 halfband filters, a

single symmetric filter of up to 256 taps, a single asymmetric

filter of up to 128 taps, or a cascade of halfband filters

followed by a programmable filter. The filter configuration is

specified by programming the Filter Configuration Register

(see Table 1).

The cascade of up to five halfband filters is an efficient

decimating filter structure. Each fixed coefficient filter in the

chain introduces a decimation of two, and the aggregate

decimation rate of the entire halfband filtering stage is given

by:

Thus, a cascade of 3 halfband filters would decimate the

input sample stream by a factor of 8.

Figure 10A is a block diagram of the halfband filter section.

The normalized frequencies for each halfband stage is

labeled. Figure 10B is an illustration of a cascaded filter

composed of five halfband filters. The final stage filter output

is clocked at FCLK/32. Since the output of each filter is at

half the rate of the input, the five halfband filter passband

characteristics can be viewed on a single plot whose X axis

is normalized to the filter output clock rate. Notice that all

halfband filters, by design, have 120dB passbands that are

less than the output rate divided by 2. Since the alias profile

is well below -120dB in the filter passband, alias concerns

are eliminated. The frequency responses of the five filters

are presented graphically in Figure 10C and in tabular form

in Table 3. Notice that the 6dB passband bandwidth (F =

0.25) is identical for all five halfband filters. The width of the

transition band, however, is different for each filter. The

transition band for the fifth halfband filter, HB5, is the

narrowest while that for the first halfband filter, HB1, is the

widest. The cascade of the halfband filters always

terminates with HB5 and is preceded by filters in order of

increasing transition bandwidth. For example, if the

HSP43124 is configured to operate with three halfbands, the

chain of filters would consist of HB3 followed by HB4 and

terminated with HB5. If only one halfband is selected, HB5 is

used.

DIN

SCLK

SYNCIN

SYNCMX

MXIN

LSB

X0

M0

MSB

LSB

MSB

FIGURE 8. DATA/MIX FACTOR SYNCHRONIZATION FOR

SERIALLY INPUT MIX FACTORS

SYNC LEADS DATA

DIN

SCLK

SYNCIN

X0

SYCNMX/

MXIN

M0

MSB

LSB

FIGURE 9. DATA/MIX FACTOR SYNCHRONIZATION

WEAVER

SYNC LEADS DATA

DECHB = 2(NUMBER OF HALFBAND FILTERS SELECTED)

(EQ. 1)

HSP43124

相关PDF资料 |

PDF描述 |

|---|---|

| HSP43168JC-33Z | IC FIR FILTER DUAL 84-PLCC |

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA188ES-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HSP43124SI40 | 制造商:Harris Corporation 功能描述: |

| HSP43124SI-40 | 制造商:Rochester Electronics LLC 功能描述:SERIAL FILTER,28 SOIC,40MHHZ,IND - Bulk |

| HSP43168 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168/883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168_07 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

发布紧急采购,3分钟左右您将得到回复。