参数资料

| 型号: | HSP43124SC-45Z |

| 厂商: | Intersil |

| 文件页数: | 5/18页 |

| 文件大小: | 0K |

| 描述: | IC I/O FILTER SER 24BIT 28-SOIC |

| 标准包装: | 26 |

| 滤波器类型: | 串行输入/输出 |

| 滤波器数: | 6 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

13

Serial Output Formatter

The Output Formatter serializes the parallel output of the

filter compute engine and generates the timing and

synchronization signals required to support a serial

interface. The Formatter produces serial data words with

programmable lengths from 8 to 32 bits. The data words

may be organized with either most or least significant bit

first. Also, the data word may be rounded or truncated to the

desired length and the format of the output data may be

specified as either two's complement or offset binary. To

simplify applications where the Serial I/O Filter is used as a

down converter, the output formatter can be configured to

scale the output by a factor of 2. The above options are

programmed via the Output Format and Output Timing

Registers detailed in Table 1.

The HSP43124 outputs a bit stream through DOUT which is

synchronous to a programmable clock signal output on

CLKOUT. The output clock, CLKOUT, is derived from FCLK

and has a programmable rate from 1 to 1/32 times FCLK.

The duty cycle of CLKOUT is 50% for rates that have an

even number of FCLKs per CLKOUT. For rates that have

and odd number of FCLKs per CLKOUT the high portion of

the CLKOUT waveform spans (n+1)/2 FCLKs and the low

portion spans (n-1)/2 FCLKs where n is the number of

FCLKs.

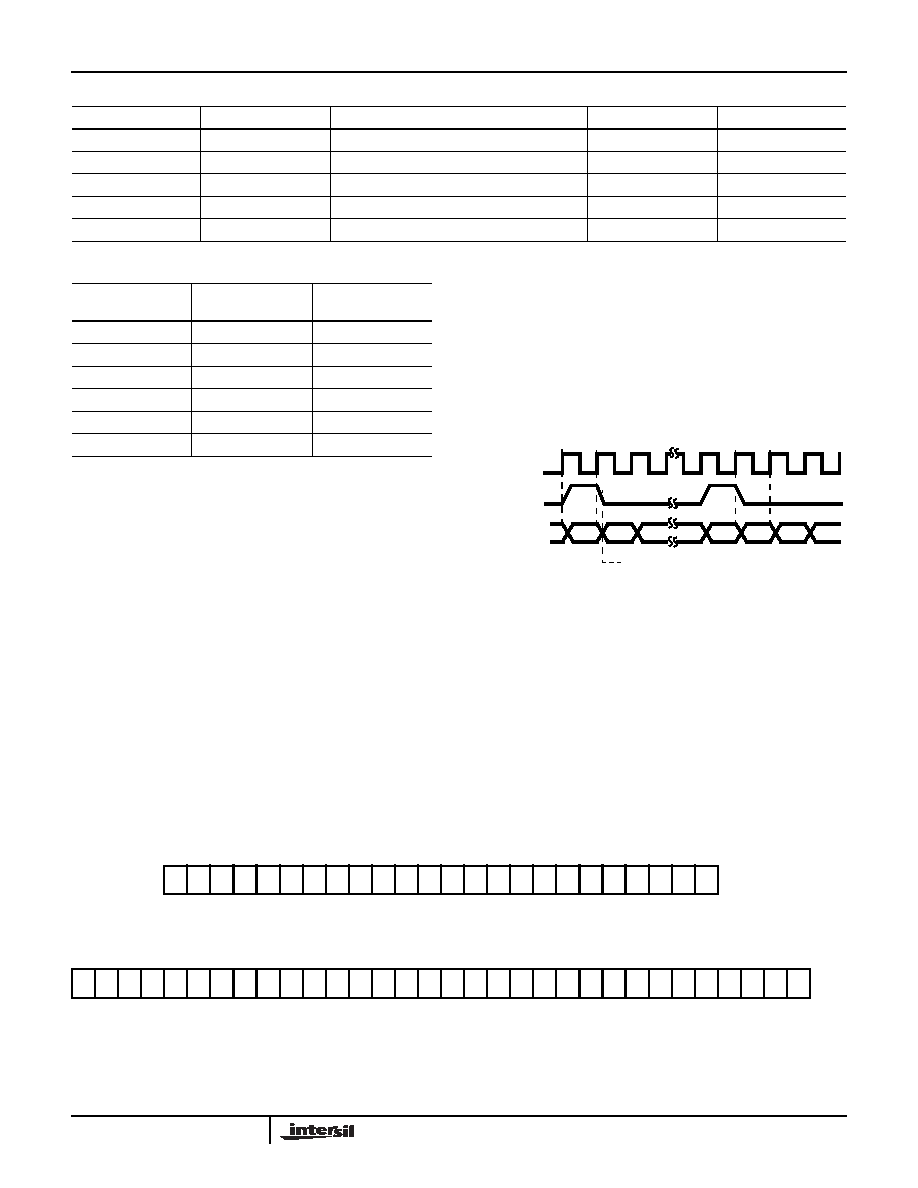

External devices synchronize to the beginning of an output

data word by monitoring SYNCOUT. This output is asserted

“high” one CLKOUT prior to the first bit of the next data word

as shown in Figure 11.

Input and Output Data Formats

The data formats for the input, output and coefficients are

fractional two’s complement. The bit weightings in the data

words are given in Figure 12. Input or output data words

programmed to have less than 24 bits, map to the most

significant bit positions of the 24-bit word. For example, an

input word defined to be 8 bits wide would map to the bit

positions with weightings from -20 to 2-7.

C30

1306852

C31

0

C32

-242570

C33

0

C34

23964

TABLE 4. HALFBAND FILTER COEFFICIENTS (32 BITS, UN-NORMALIZED) (Continued)

COEFFICIENT

HALFBAND #1

HALFBAND #2

HALFBAND #3

HALFBAND #4

HALFBAND #5

TABLE 5. PERFORMANCE ENVELOPE PARAMETERS

NUMBER OF

HALFBANDS

HBCLKS

DECHB

00

1

113

2

233

4

369

8

4

125

16

5

221

32

LSB

MSB

LSB

MSB

CLKOUT

DOUT

SYNCOUT

NOTE: Assumes data is being output LSB first.

FIGURE 11. SERIAL OUTPUT TIMING

SYNC LEADS DATA

FRACTIONAL TWO’S COMPLEMENT FORMAT FOR 24-BIT INPUT AND OUTPUT

24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 987

6543

21

-20

. 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-102-112-122-132-142-152-162-172-182-192-202-212-222-23

FRACTIONAL TWO’S COMPLEMENT FORMAT FOR 32-BIT COEFFICIENTS

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 987

6543

21

-20

. 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-102-112-122-132-142-152-162-172-182-192-202-212-222-232-242-252-262-272-282-292-302-31

NOTE: The negative sign on the MSB implies 2’s complement formt.

FIGURE 12. DATA FORMATS

HSP43124

相关PDF资料 |

PDF描述 |

|---|---|

| HSP43168JC-33Z | IC FIR FILTER DUAL 84-PLCC |

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA188ES-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HSP43124SI40 | 制造商:Harris Corporation 功能描述: |

| HSP43124SI-40 | 制造商:Rochester Electronics LLC 功能描述:SERIAL FILTER,28 SOIC,40MHHZ,IND - Bulk |

| HSP43168 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168/883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168_07 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

发布紧急采购,3分钟左右您将得到回复。