参数资料

| 型号: | HSP43124SC-45Z |

| 厂商: | Intersil |

| 文件页数: | 2/18页 |

| 文件大小: | 0K |

| 描述: | IC I/O FILTER SER 24BIT 28-SOIC |

| 标准包装: | 26 |

| 滤波器类型: | 串行输入/输出 |

| 滤波器数: | 6 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 管件 |

10

The coefficient set for each of the halfband filters is given in

Table 4. These values are the 32-bit, two’s complement,

integer representation of the filter coefficients. Scaling these

values by 2-31 yields the fractional two’s complement

coefficients used to achieve unity gain in the Filter Processor.

If a specific frequency response is desired, a programmable

FIR filter may be activated. The filter compute engine takes

advantage of symmetry in FIR coefficients is by summing

data samples sharing a common coefficient prior to

multiplication. In this manner, two filter taps are calculated

per multiply accumulate cycle. If an asymmetric filter is

specified, only one tap per multiply accumulate cycle is

calculated.

The processing rate of the Filter Compute Engine is

proportional to FCLK. As a result, the frequency of FCLK

must exceed a minimum value to insure that a filter

calculation is complete before the result is required for

output. In configurations which do not use decimation, one

input sample period is available for filter calculation before

an output is required. For configurations which employ

decimation, up to 256 input sample periods may be available

for filter calculation. The following equation specifies the

minimum FCLK rate required for configurations which use

the programmable filter as an FIR filter.

In this equation FS is the input sample rate (SCLK/# Bits in

SER word), TAPS is the number of taps in the FIR filter (0 to

256), DECFIR is the decimation rate of the programmable

FIR (1 to 8), HBCLKS is a compute clock factor based on the

number of halfband filters in the configuration (see Table 5),

and DECHB is the aggregate decimation rate for the

cascade of halfband filters (see Table 5). For example, if the

input sample rate is 800kHz, a 128 tap FIR filter with no

decimation is selected, and a cascade of 2 halfband filters is

used, calculate the minimum FCLK rate as follows:

Thus, the Min FCLK is 19.6MHz.

NOTE: For configurations in which the halfband filters are

used, the FCLK rate must exceed 14FS.

The longest length FIR filter realizable for a particular

configuration is determined by solving the above equation

for TAPS. The resulting expression is given below.

The maximum throughput sample rate may be specified by

solving the above equation for FS. The resulting equation is

NOTE: For configurations using filters with asymmetric coeffi-

cients, the term TAPS in the above equations should be multi-

plied by two in order to determine the correct FCLK.

The Filter Compute Engine is synchronized with an incoming

data stream by asserting the FSYNC input. When this input

is sampled low by the rising edge of FCLK, the Compute

Engine is reset, and the data word following the next

assertion of SYNCIN is recognized as the first data sample

input to the filter structure.

Min FCLK

FS

DECHB

--------------------

TAPS/(2*DECFIR) HBCLKS 1

++

()

or at least14FS when Halfbands are used

=

(EQ. 2)

(EQ. 3)

Min FCLK

800kHz

4

---------------------

128

2

1

----------

33 1

++

200kHz

() 64 33 1

++

[] 19.6MHz

=

or at least 14 (800kHz)

11.2MHz

=

=

Max TAPS = 2DECFIR((FCLK/FS)DECHB - HBCLKS - 1)

(EQ. 4)

Max FS = FCLK*DECHB /(TAPS/(2*DECFIR) + HBCLKS + 1). (EQ. 5)

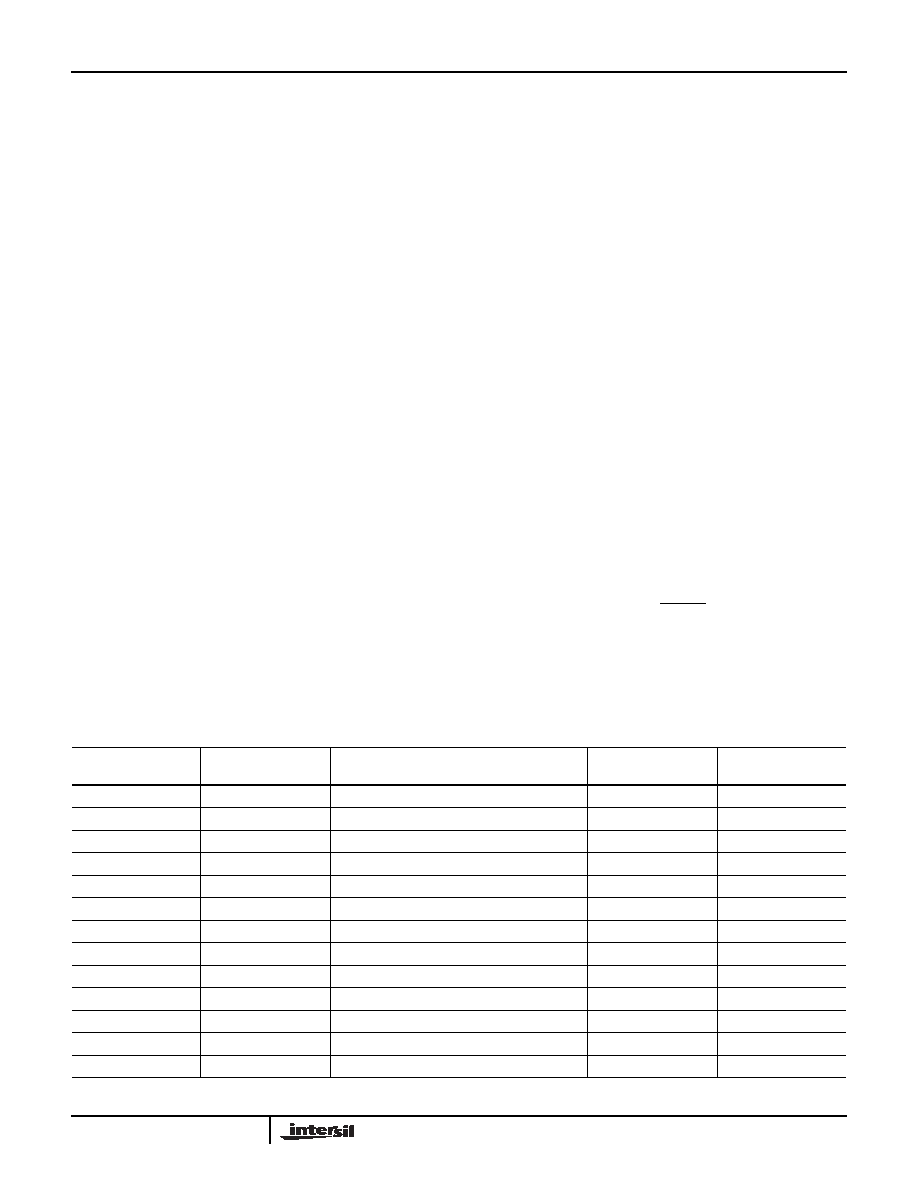

TABLE 3. FREQUENCY RESPONSE OF HALFBAND FILTERS

NORMALIZED

FREQUENCY

HALFBAND

#1

HALFBAND

#2

HALFBAND

#3

HALFBAND

#4

HALFBAND

#5

0.000000

-0.000000

0.000000

-0.000000

0.007812

0.000000

-0.000000

0.015625

-0.000113

-0.000000

0.023438

-0.000677

-0.000006

-0.000000

0.031250

-0.002243

-0.000052

-0.000000

0.039062

-0.005569

-0.000227

-0.000000

0.000000

0.046875

-0.011596

-0.000719

-0.000001

0.000000

-0.000000

0.054688

-0.021433

-0.001859

-0.000009

-0.000000

0.062500

-0.036333

-0.004165

-0.000041

-0.000000

0.070312

-0.057670

-0.008391

-0.000149

-0.000001

-0.000000

0.078125

-0.086916

-0.015557

-0.000448

-0.000012

-0.000000

0.085938

-0.125619

-0.026983

-0.001175

-0.000066

-0.000000

0.093750

-0.175382

-0.044301

-0.002767

-0.000258

-0.000000

HSP43124

相关PDF资料 |

PDF描述 |

|---|---|

| HSP43168JC-33Z | IC FIR FILTER DUAL 84-PLCC |

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA188ES-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HSP43124SI40 | 制造商:Harris Corporation 功能描述: |

| HSP43124SI-40 | 制造商:Rochester Electronics LLC 功能描述:SERIAL FILTER,28 SOIC,40MHHZ,IND - Bulk |

| HSP43168 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168/883 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

| HSP43168_07 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual FIR Filter |

发布紧急采购,3分钟左右您将得到回复。