- 您现在的位置:买卖IC网 > PDF目录67682 > IBM25PPC405GPR3BB400Z 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 PDF资料下载

参数资料

| 型号: | IBM25PPC405GPR3BB400Z |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| 封装: | 35 X 35 MM, ENHANCED, PLASTIC, BGA-456 |

| 文件页数: | 29/58页 |

| 文件大小: | 1264K |

| 代理商: | IBM25PPC405GPR3BB400Z |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

Preliminary

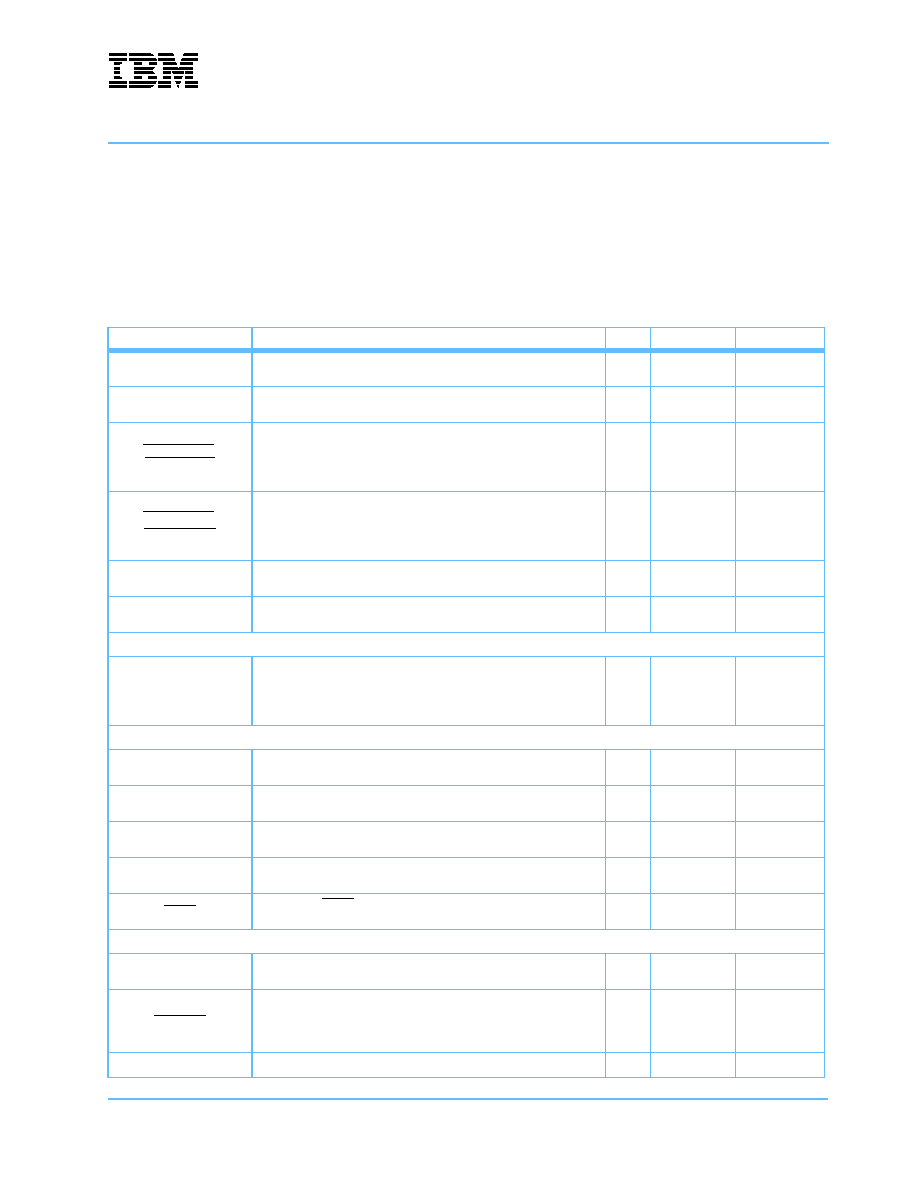

PowerPC 405GPr Embedded Processor Data Sheet

3/14/03

Page 35 of 58

UART1_Rx

UART1 Serial Data In.

I

5V tolerant

3.3V LVTTL

1

UART1_Tx

UART1 Serial Data Out.

O

5V tolerant

3.3V LVTTL

6

UART1_DSR/

UART1_CTS

UART1 Data Set Ready

or

UART1 Clear To Send. To access this function, software must

toggle a DCR bit.

I

5V tolerant

3.3V LVTTL

1

UART1_RTS/

UART1_DTR

UART1 Request To Send

or

UART1 Data Terminal Ready. To access this function, software

must toggle a DCR bit.

O

5V tolerant

3.3V LVTTL

6

IICSCL

IIC Serial Clock.

I/O

5V tolerant

3.3V LVTTL

1, 2

IICSDA

IIC Serial Data.

I/O

5V tolerant

3.3V LVTTL

1, 2

Interrupts Interface

IRQ0:6[GPIO17:23]

Interrupt requests

or

General Purpose I/O. To access this function, software must

toggle a DCR bit.

I[I/O]

5V tolerant

3.3V LVTTL

1

JTAG Interface

TDI

Test data in.

I

5V tolerant

3.3V LVTTL

1, 4

TMS

JTAG test mode select.

I

5V tolerant

3.3V LVTTL

1, 4

TDO

Test data out.

O

5V tolerant

3.3V LVTTL

TCK

JTAG test clock. The frequency of this input can range from DC to

25MHz.

I

5V tolerant

3.3V LVTTL

1, 4

TRST

JTAG reset. TRST must be low at power-on to initialize the JTAG

controller and for normal operation of the PPC405GPr.

I

5V tolerant

3.3V LVTTL

5

System Interface

SysClk

Main system clock input.

I

5V tolerant

3.3V LVTTL

SysReset

Main system reset. External logic can drive this bidirectional pin

low (minimum of 16 cycles) to initiate a system reset. A system

reset can also be initiated by software. Implemented as an open-

drain output (two states; 0 or open circuit).

I/O

5V tolerant

3.3V LVTTL

1, 2

AVDD

Clean voltage input for the PLL.

I

Signal Functional Description (Part 6 of 8)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball.

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-Up and Pull-Down Resistors” on page 29 for recommended termination values.

3. Must pull down. See “Pull-Up and Pull-Down Resistors” on page 29 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Bus Control Signals” on page 29.

Signal Name

Description

I/OType

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| IBM25PPC405GPR3DB266 | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC603E-BX-133X | 32-BIT, 133 MHz, RISC PROCESSOR, CBGA255 |

| IBM25PPC603EV-FX-233X | 32-BIT, 233 MHz, RISC PROCESSOR, CQFP240 |

| IBM25PPC603EV-FX-225X | 32-BIT, 225 MHz, RISC PROCESSOR, CQFP240 |

| IBM25PPC603EV-BX-233X | 32-BIT, 233 MHz, RISC PROCESSOR, CBGA255 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IBM25PPC405-GPR-3JB266Z | 制造商:IBM 功能描述: |

| IBM25PPC405GPR-3KB266C | 制造商:IBM 功能描述: |

| IBM25PPC440GX3CB667C | 制造商:IBM 功能描述: |

| IBM25PPC603E-BX-080-X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:32-Bit Microprocessor |

| IBM25PPC603E-BX-100-X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:32-Bit Microprocessor |

发布紧急采购,3分钟左右您将得到回复。