- 您现在的位置:买卖IC网 > PDF目录2070 > ICS1562BM-201T (IDT, Integrated Device Technology Inc)IC VIDEO CLK SYNTHESIZER 16-SOIC PDF资料下载

参数资料

| 型号: | ICS1562BM-201T |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 9/20页 |

| 文件大小: | 0K |

| 描述: | IC VIDEO CLK SYNTHESIZER 16-SOIC |

| 产品变化通告: | Product Discontinuation 13/May/2009 |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器,时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,TTL,晶体 |

| 输出: | CMOS,PECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 260MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

| 其它名称: | 1562BM-201T |

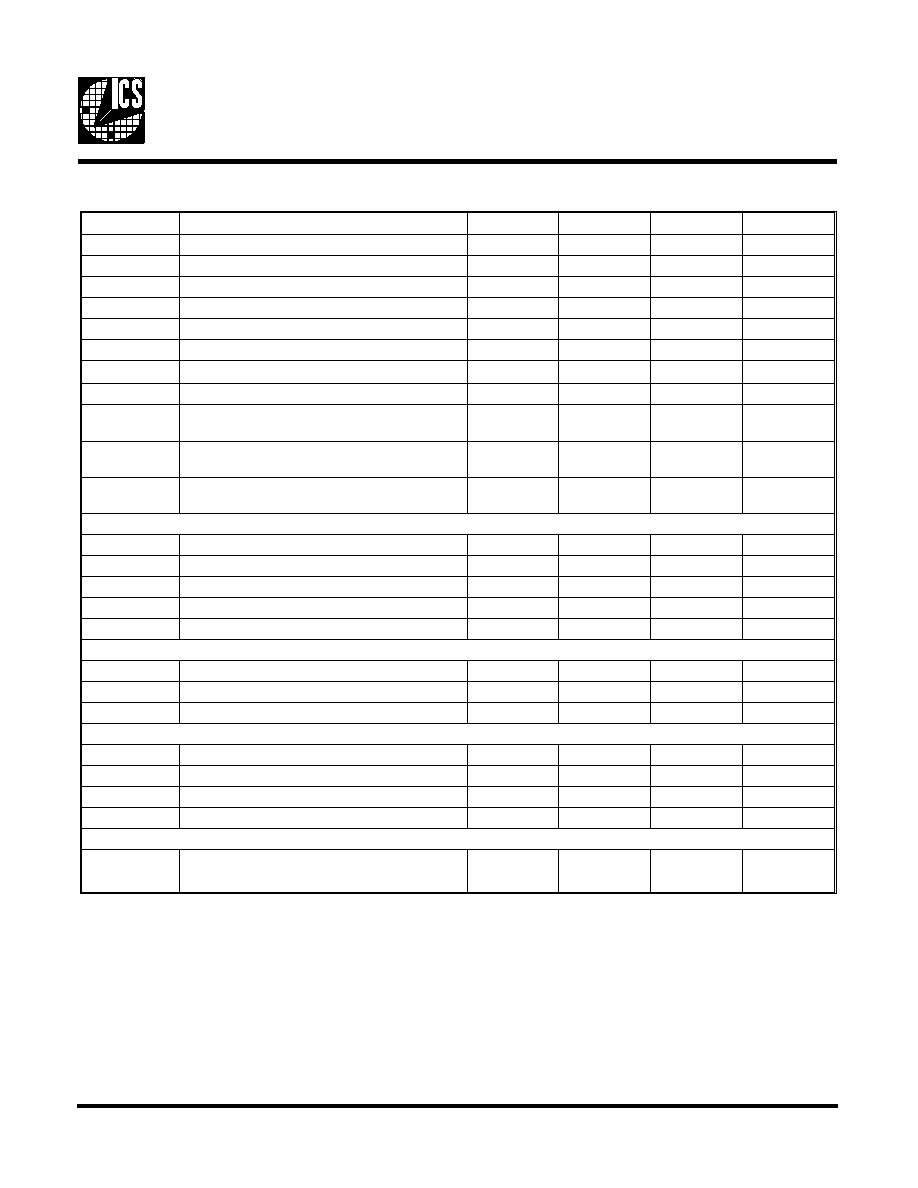

AC Characteristics

SYMBOL

PARAMETER

MIN

TYP

MAX

UNITS

Fvco

VCO Frequency (see Note 1)

40

260

MHz

Fxtal

Crystal Frequency

5

20

MHz

Cpar

Crystal Oscillator Loading Capacitance

20

pf

Fload

LOAD Frequency

80

MHz

Txhi

XTAL1 High Time (when driven externally)

8

ns

Txlo

XTAL1 Low Time (when driven externally)

8

ns

Tlock

PLL Acquire Time (to within 1%)

500

s

Idd

VDD Supply Current

15

t.b.d.

mA

Iddo

VDDO Supply Current (excluding CLK+/

termination)

20

t.b.d.

mA

Thigh

Differential Clock Output Duty Cycle

(see Note 2)

45

55

%

Jclk

Differential Clock Output Cumulative Jitter

(see Note 3)

<0.06

pixel

DIGITAL INPUTS - ICS1562B-001

1

Address Setup Time

10

ns

2

Address Hold Time

10

ns

3

Data Setup Time

10

ns

4

Data Hold Time

10

ns

5

STROBE Pulse Width (Thi or Tlo)20

ns

DIGITAL INPUTS - ICS1562B-201

6

DATA/HOLD~ Setup Time

10

ns

7

DATA/HOLD~ Hold Time

10

ns

8

DATCLK Pulse Width (Thi or Tlo)20

ns

PIPELINE DELAY RESET

9

Reset Activation Time

2*Tclk

ns

10

Reset Duration

4*Tload

ns

11

Restart Delay

2*Tload

ns

12

Restart Matching

-1*Tclk

+1.5*Tclk

ns

DIGITAL OUTPUTS

13

CLK+/CLK

Clock Rate

260

MHz

14

LOAD To LD/N2 Skew (Shift Clock Mode)

-2

0

+2

ns

Note 1: Use of the post-divider is required for frequencies lower than 40 MHz on CLK+ & CLK- outputs. Use of the post-divider

is recommended for output frequencies lower than 65 MHz.

Note 2: Using load circuit of Figure 6. Duty cycle measured at zero crossings of difference voltage between CLK+ and CLK-.

Note 3: Cumulative jitter is defined as the maximum error (in the domain) if any CLK edge, at any point in time, compared with

the equivalent edge generated by an ideal frequency source.

ICS laboratory testing indicates that the typical value shown above can be treated as a maximum jitter specification in

virtually all applications. Jitter performance can depend somewhat on circuit board layout, decoupling, and register

programming.

ICS1562B

17

相关PDF资料 |

PDF描述 |

|---|---|

| ICS1574BMT | IC CLOCK GEN PROGR LASER 16-SOIC |

| ICS180M-01LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-02LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-03LF | IC CLOCK GEN LOW EMI 8-SOIC |

| ICS181M-51LF | IC CLOCK GEN LOW EMI 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS1562BM-XXX | 制造商:ICS 制造商全称:ICS 功能描述:User Programmable Differential Output Graphics Clock Generator |

| ICS1567 | 制造商:ICS 制造商全称:ICS 功能描述:Differential Output Video Dot Clock Generator |

| ICS1567-742 | 制造商:ICS 制造商全称:ICS 功能描述:Differential Output Video Dot Clock Generator |

| ICS1567M-742 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Video/Graphics Clock Generator |

| ICS1572 | 制造商:ICS 制造商全称:ICS 功能描述:User Programmable Differential Output Graphics Clock Generator |

发布紧急采购,3分钟左右您将得到回复。