- 您现在的位置:买卖IC网 > PDF目录175707 > ICS5342-2 Analog IC PDF资料下载

参数资料

| 型号: | ICS5342-2 |

| 英文描述: | Analog IC |

| 中文描述: | 模拟IC |

| 文件页数: | 26/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

ICS5342

GENDAC

32

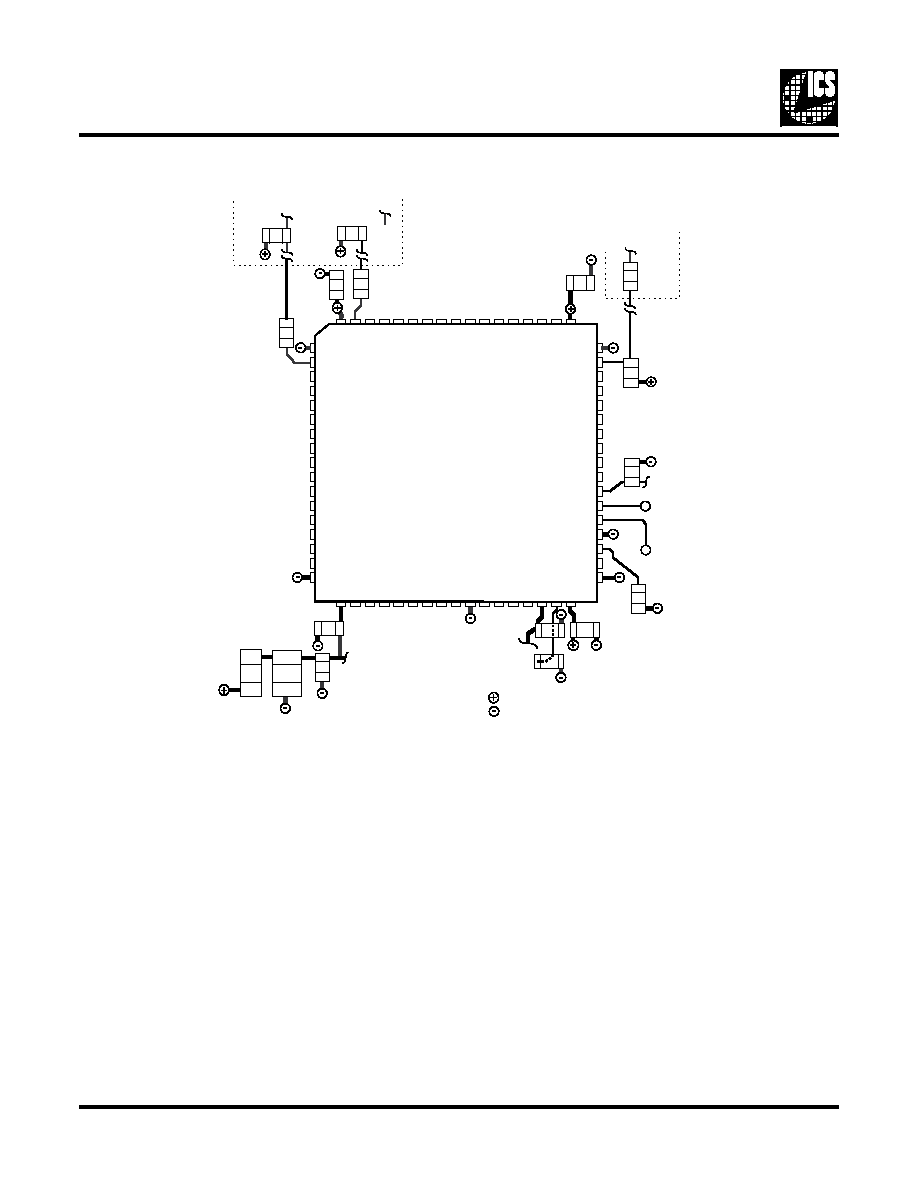

Recommended Layout

VIA to power plane

VIA to ground plane

AGND

RED

AVDD

CVDD

GRN

BLUE

RSET

DVDD

PCLK

XVDD

XGND

XOUT

XIN

CLK0

36

35

34

33

32

31

30

29

28

27

40

39

38

37

43

42

41

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

1

2

3

4

5

6

7

8

9

68

64

65

66

67

61

62

63

GENDAC II

ICS5342

CLK1

DGND

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

R4

R2

R4

R5

R1

C2

VAA

C1

FB1

C3

-

+

C1 0.047

F chip capacitor

C2 0.1

F chip capacitor

C3 10

F tantalum capacitor

FB1 ferrite bead, Fair-Rite 2743019447

R1 33 ohm

R2 100 ohm

R3 141 ohm, 1%

R4 220 ohm

R5 560 ohm

Y1 parallel resonant crystal cut for C

L = 12 pF

C2

LOCATE NEAR

CONTROLLER

LOCATE NEAR

CONTROLLER

C1

C2

R3

VAA

C2

Y1

VAA

C2

VREF

CGND

DGND

CVDD

CGND

5342_30

Board Layout and Analog Signal Consider-

ations

The high performance of the GENDAC is dependent on care-

ful PC board layout. The use of a four layer board (internal

power and ground planes, signals on the two surface layers) is

recommended. The ground plane layer should be closest to the

component side of the board. The layout following this sec-

tion shows a suggested configuration.

Power Supply

As a high speed CMOS device, the GENDAC may draw large

transient currents from the power supply. It is necessary to

adopt high-frequency board-layout and power-distribution

techniques to assure proper operation of the GENDAC. This

will also minimize radio frequency interference (RFI). DAC

to DAC crosstalk can also be attributed to a high impedance

power supply.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS5342-3 | Analog IC |

| ICS9111M-06 | Miscellaneous Clock Generator |

| ICS9117M02 | Peripheral IC |

| ICS9118M-02 | Miscellaneous Clock Generator |

| ICS9118M-04 | Miscellaneous Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342-3 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| ICS541 | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

| ICS541M | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

发布紧急采购,3分钟左右您将得到回复。