- 您现在的位置:买卖IC网 > PDF目录175707 > ICS5342-2 Analog IC PDF资料下载

参数资料

| 型号: | ICS5342-2 |

| 英文描述: | Analog IC |

| 中文描述: | 模拟IC |

| 文件页数: | 7/36页 |

| 文件大小: | 1017K |

| 代理商: | ICS5342-2 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

ICS5342

GENDAC

15

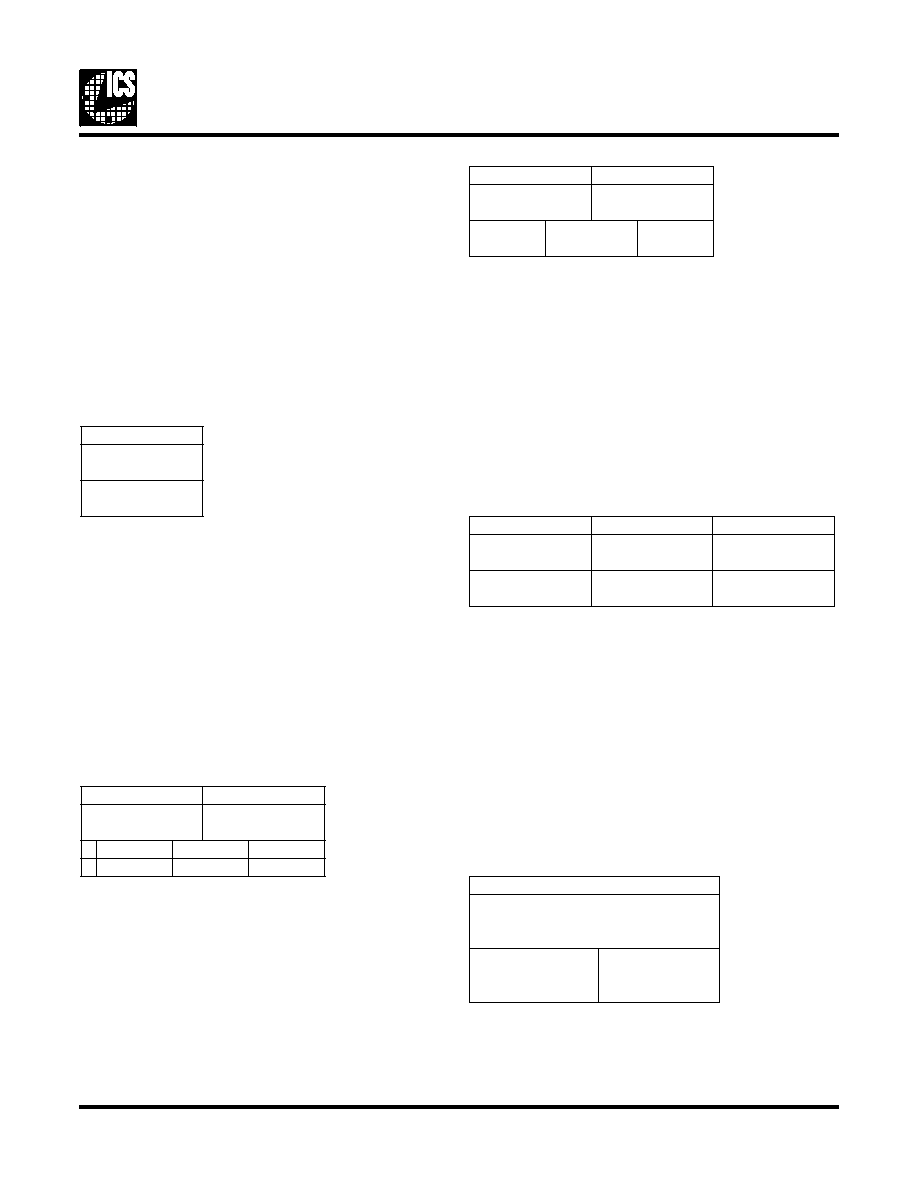

Color Modes

The nine selectable color modes are described here. Four are

eight-bit and five are 16-bit wide pixel input. Color Modes 0-3

are 8-bit interfaces with bits P0-P7; P8-P15 are “don’t care”

bits.

Mode 0: 8-bit Pseudo Color (one clock per pixel). This mode

is the 8-bit per pixel Pseudo Color mode. In this mode, inputs

P0-P7 are the pixel address for the color palette RAM and are

latched on the rising edge of every PCLK. This is the default

mode on power up and it is selected by setting bits CR7-CR4

to 0000.

Mode 1: (15-bit per color bypass Hi-Color mode). This mode

is the 15-bit per pixel bypass mode. In this mode, inputs P0-P7

are the color DATA and are input directly to the DAC, by-

passing the color palette. The two bytes of data are latched in

two successive PCLK rising edges. ICS5342 supports only

the two clock mode and does not support the mode where the

data are latched on the rising and the falling edges. For com-

patibility, the 15/16 one clock modes are selected as two clock

modes in this chip. The low-byte, high byte synchronization

is internally done by the rising edge of BLANK*. Each color

is 5-bit wide and is packed into two bytes as shown below.

This mode can be selected by setting bits CR7-CR4 to 0010,

1000 or 1010.

3LSB = set to zero

Mode 2: (16-bit per pixel bypass XGA mode). This mode is

the 16-bit per pixel bypass mode and the P0-P7 inputs to go to

the DAC directly, bypassing the color palette. The 2 bytes

data is latched on two successive rising edges and the low-

byte, high-byte synchronization is internally done by the ris-

ing edge of BLANK*. In this mode, blue and red colors are 5

bits wide and green is 6 bits wide. The 2 bytes of data are

packed as shown below. This mode can be selected by setting

bits CR7-CR4 to 0110 or 1100.

2LSB = set to zero (green)

3LSB = set to zero (blue, red)

Mode 3: (24-bit per pixel True Color Mode). This mode is the

24-bit per pixel bypass mode. The three bytes of data are

latched on three successive PCLK edges and the first byte is

synchronized by the rising edge of BLANK*. In this mode,

each of the colors are 8-bit wide and the DAC is an 8-bit wide

DAC. The first byte is blue followed by green and red. This

mode can be selected by setting bits CR7-CR4 to 0100 or

1110. The DAC outputs changes every three cycles and the

pipeline delay from the first byte to output is five cycles.

16 bit Color Modes

Modes 4 - 8 use the 16-bit pixel interface.

Mode 4: (8-bit Pseudo Color two pixels per clock) In this

mode, inputs P0-P15 are latched on the rising edge of every

PCLK. P0-7 and P8-P15 are used for successive addresses for

the palette RAM using an internal clock (ICLK) that runs at

twice the PCLK frequency. The DAC outputs change twice

for every PCLK and the pipeline delay from the first word to

output is one and one half cycles. This mode can be selected

by setting bits CR7-CR4 to 0001.

Mode 5: (16-bit pixel interface, 15-bit per color bypass Hi-

Color Mode) In this mode inputs P0-P15 are the color data

and are input directly to the DAC, bypassing the color palette.

The data is latched by the rising edge of PCLK and is pipe-

8-bit Pseudo Color

- Mode 0

PIXEL BYTE

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

76543210

LUT ADDRESS

15-Bit Color - Mode 1

SECOND BYTE

FIRST BYTE

PPPPPPPPPPPPPPPP

7654321076543210

X 765437654376543

X RED

GREEN

BLUE

16-Bit Color - Mode 2

SECOND BYTE

FIRST BYTE

PPPPPPPPPPPPPPPP

7654321076543210

7654376543276543

RED

GREEN

BLUE

24-bit Color - Mode 3

THIRD BYTE

SECOND BYTE

FIRST BYTE

PPPPPPPPPPPPPPPPPPPPPPPP

765432107654321076543210

RED

GREEN

BLUE

Multiplexed 8-bit Pseudo Color Word

- Mode 4

PIXEL WORD

PPPPPP P P PPPPPPPP

111111 9 8 76543210

543210

765432 1 0 76543210

2nd PIXEL

ADDRESS

1st PIXEL

ADDRESS

相关PDF资料 |

PDF描述 |

|---|---|

| ICS5342-3 | Analog IC |

| ICS9111M-06 | Miscellaneous Clock Generator |

| ICS9117M02 | Peripheral IC |

| ICS9118M-02 | Miscellaneous Clock Generator |

| ICS9118M-04 | Miscellaneous Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS5342-3 | 制造商:ICS 制造商全称:ICS 功能描述:Analog IC |

| ICS5342ADD | 制造商:ICS 制造商全称:ICS 功能描述:Addendum to ICS5342 Data Sheet |

| ICS5342V | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

| ICS541 | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

| ICS541M | 制造商:ICS 制造商全称:ICS 功能描述:PRELIMINARY INFORMATION PLL Clock Divider |

发布紧急采购,3分钟左右您将得到回复。