- 您现在的位置:买卖IC网 > PDF目录67710 > ICSSSTUA32S865AHLF-T (INTEGRATED DEVICE TECHNOLOGY INC) SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 PDF资料下载

参数资料

| 型号: | ICSSSTUA32S865AHLF-T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 锁存器 |

| 英文描述: | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| 封装: | 9 X 13 MM, LEAD FREE, BGA-160 |

| 文件页数: | 4/17页 |

| 文件大小: | 199K |

| 代理商: | ICSSSTUA32S865AHLF-T |

12

ICSSSTUA32S865A

1053A—03/21/05

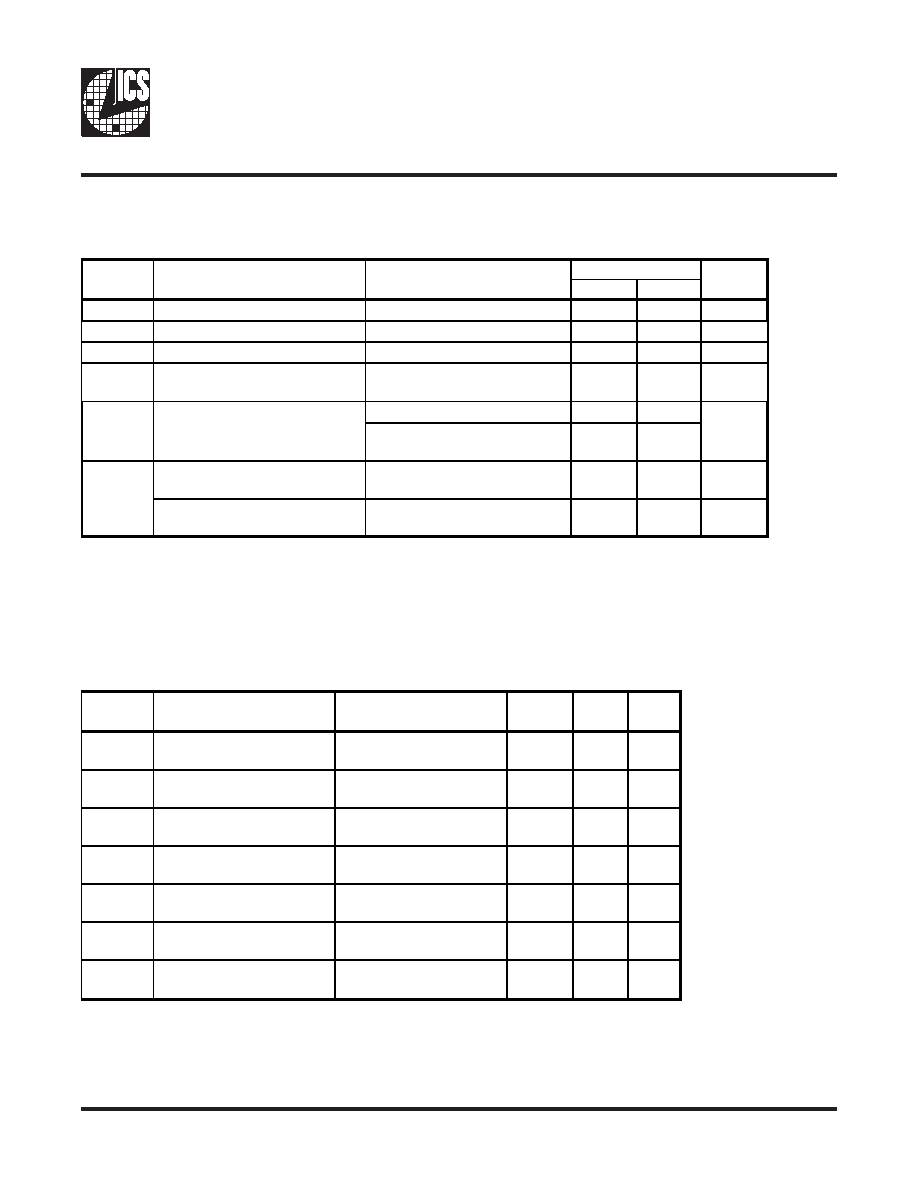

Switching Characteristics

(over recommended operating free-air temperature range, unless otherwise noted)

Symbol

Parameter

Measurement

Conditions

MIN

MAX

Units

fmax

Max input clock frequency

410

MHz

tPDM

Propagation delay, single

bit switching

CK

↑ to CK#↓ QN

1.25

1.9

ns

tLH

Low to High propagation

delay

CK

↑ to CK#↓ to

PTYERR#

1.2

3

ns

tHL

High to low propagation

delay

CK

↑ to CK#↓ to

PTYERR#

13

ns

tPDMSS

Propagation delay

simultaneous switching

CK

↑ to CK#↓ QN

2

ns

tPHL

High to low propagation

delay

Reset#

↓ to QN↓

3ns

tPLH

Low to High propagation

delay

Reset#

↓ to PTYERR#↑

3ns

1. Guaranteed by design, not 100% tested in production.

Timing Requirements

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

MAX

fclock

Clock frequency

410

MHz

tW

Pulse duration

1

ns

tACT

Differential inputs active time

10

ns

tINACT

Differential inputs inactive time

15

ns

tS

Data before CLK

↑, CLK#↓

0.5

DCS0, DSC1# before CK

↑,

CK#

↓, CSR# high

0.7

Hold time

DCS#, DODT, DCKE and Q

after CK

↑, CK#↓

0.50

ns

Hold time

PAR_IN after CK

↑, CK#↓

0.50

ns

1 - Guaranteed by design, not 100% tested in production.

2 - For data signal input slew rate of 1V/ns.

4 - CLK/CLK# signal input slew rate of 1V/ns.

SYMBOL

Notes:

tH

3 - For data signal input slew rate of 0.5V/ns and < 1V/ns.

VDD = 1.8V ±0.1V

UNITS

PARAMETERS

ns

Setup time

相关PDF资料 |

PDF描述 |

|---|---|

| ICSSSTUB32871AHMLFT | 32871 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYH-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864YHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICSSSTUA32S869B | 制造商:ICS 制造商全称:ICS 功能描述:14-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUAF32865A | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32865AHLFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866B | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

| ICSSSTUAF32866BHLFT | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2 |

发布紧急采购,3分钟左右您将得到回复。