- 您现在的位置:买卖IC网 > Datasheet目录329 > IDT70V5388S166BGI (IDT, Integrated Device Technology Inc)IC SRAM 1.125MBIT 166MHZ 272BGA Datasheet资料下载

参数资料

| 型号: | IDT70V5388S166BGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/29页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 1.125MBIT 166MHZ 272BGA |

| 标准包装: | 20 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 四端口,同步 |

| 存储容量: | 1.125M(64K x 18) |

| 速度: | 166MHz |

| 接口: | 并联 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 272-BBGA |

| 供应商设备封装: | 272-PBGA(27x27) |

| 包装: | 托盘 |

| 其它名称: | 70V5388S166BGI |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

�� �

�

�

�IDT70V5388/78�

�3.3V� 64/32K� x� 18� Synchronous� FourPort?� Static� RAM�

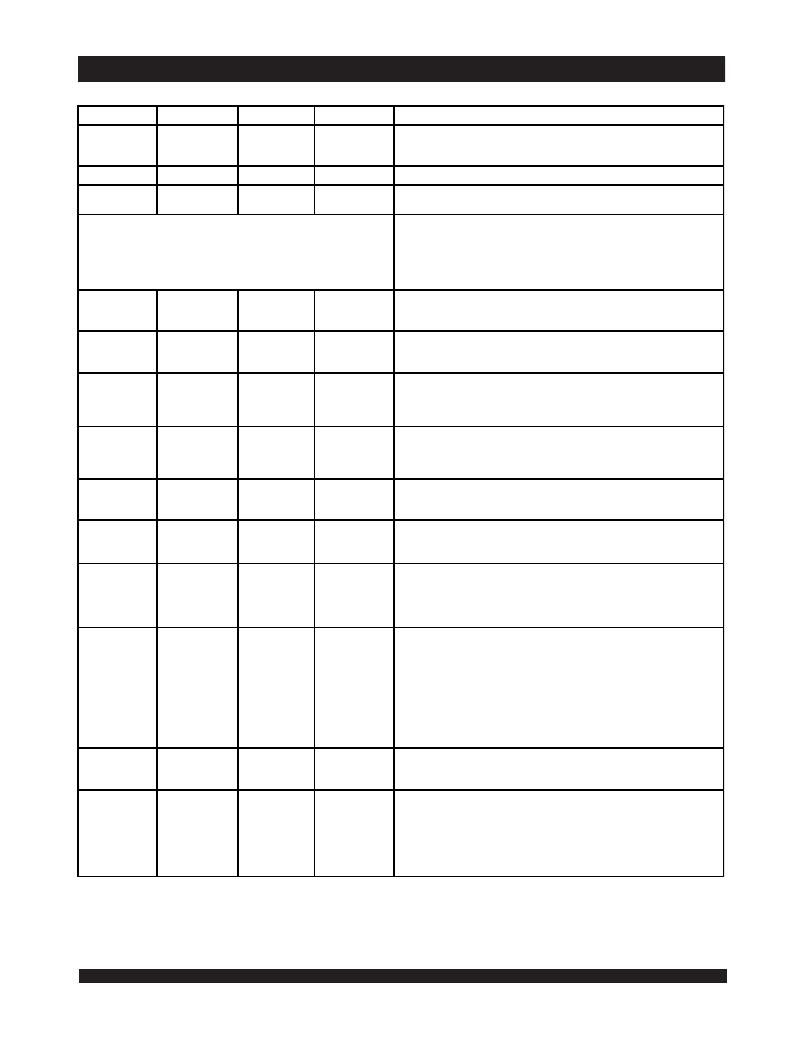

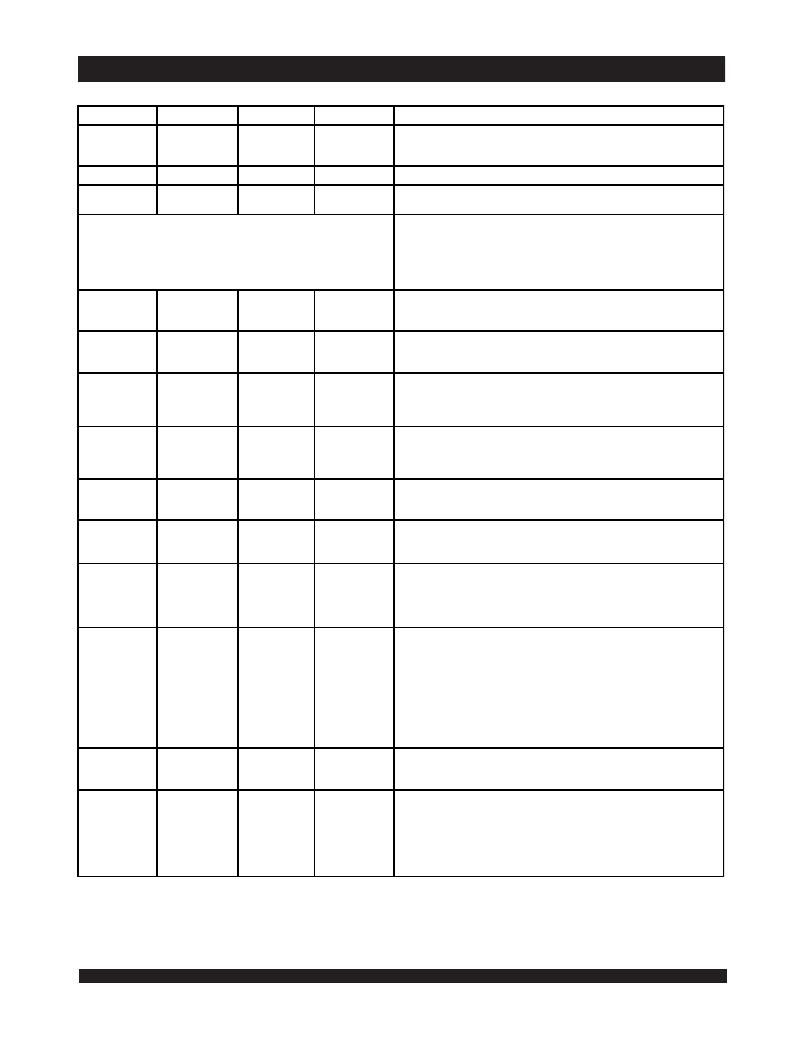

�Pin� Definitions�

�Industrial� and� Commercial� Temperature� Ranges�

�Port� 1�

�Port� 2�

�Port� 3�

�Port� 4�

�Description�

�Address� Inputs.� In� the� CNTRD� and� MKRD� operations,� these� pins� serve�

�A� 0P1� -� A� 15P1� (1)�

�A� 0P2� -� A� 15P2� (1)�

�A� 0P3� -� A� 15P3� (1)�

�A� 0P4� -� A� 15P4� (1)�

�as� outputs� for� the� internal� address� counter� and� the� internal� counter� mask�

�register� respectively.�

�I/O� 0P1� -� I/O� 17P1�

�CLK� P1�

�I/O� 0P2� -� I/O� 17P2�

�CLK� P2�

�I/O� 0P3� -� I/0� 17P3�

�CLK� P3�

�I/O� 0P4� -� I/O� 17P4�

�CLK� P4�

�Data� Bus� Input/Output.�

�Clock� Input.� The� maximum� clock� input� rate� is� f� MAX� .� The� clock� signal� can�

�be� free� running� or� strobed� depending� on� system� requirements.�

�Master� Reset� Input.� MRST� is� an� asycnchronous� input,� and� affects� all�

�MRST�

�ports.� It� must� be� asserted� LOW� (� MRST� =� V� IL� )� at� initial� power-up.� Master�

�Reset� sets� the� internal� value� of� all� address� counters� to� zero,� and� sets�

�the� counter� mask� registers� for� each� port� to� 'unmasked'.� It� also� resets� the�

�output� flags� for� the� mailboxes� and� the� counter� interrupts� (� INT� =� CNTINT�

�=� V� IH� )� and� deselects� all� registered� control� signals.�

�CE� 0P1� ,� CE� 1P1�

�CE� 0P2� ,� CE� 1P2�

�CE� 0P3� ,� CE� 1P3�

�CE� 0P4� ,� CE� 1P4�

�Chip� Enable� Inputs.� To� activate� any� port,� both� signals� must� be� asserted�

�to� their� active� states� (� CE� 0� =� V� IL� ,� CE� 1� =� V� IH� ).� A� given� port� is� disabled� if�

�either� chip� enable� is� deasserted� (� CE� 0� =� V� IH� and/or� CE� 1� =� V� IL� ).�

�R/� W� PI�

�R/� W� P2�

�R/� W� P3�

�R/� W� P4�

�Read/Write� Enable� Input.� This� signal� is� asserted� LOW� (R/� W� =� V� IL� )� in�

�order� to� write� to� the� FourPort� memory� array,� and� it� is� asserted� HIGH�

�(R/� W� =� V� IH� )� in� order� to� read� from� the� array.�

�LB� P1�

�LB� P2�

�LB� P3�

�LB� P4�

�Lower� Byte� Select� Input� (I/O� 0� -� I/O� 8� ).� Asserting� this� signal� LOW� (� LB� =� V� IL� )�

�enables� read/write� operations� to� the� lower� byte.� For� read� operations,� this�

�signal� is� used� in� conjunction� with� OE� in� order� to� drive� output� data� on� the�

�lower� byte� of� the� data� bus.�

�UB� P1�

�UB� P2�

�UB� P3�

�UB� P4�

�Upper� Byte� Select� Input� (I/O� 9� -� I/O� 17� ).� Asserting� this� signal� LOW� (� LB� =�

�V� IL� )� enables� read/write� operations� to� the� upper� byte.� For� read�

�operations,� this� signal� is� used� in� conjunction� with� OE� in� order� to� drive�

�output� data� on� the� upper� byte� of� the� data� bus.�

�OE� P1�

�OE� P2�

�OE� P3�

�OE� P4�

�Output� Enable� Input.� Asserting� this� signal� LOW� (� OE� =� V� IL� )� enables� the�

�device� to� drive� data� on� the� I/O� pins� during� read� operation.� OE� is� an�

�asychronous� input.�

�CNTLD� P1�

�CNTLD� P2�

�CNTLD� P3�

�CNTLD� P4�

�Counter� Load� Input.� Asserting� this� signal� LOW� (� CNTLD� =� V� IL� )� loads� the�

�address� on� the� address� lines� (A� 0� -� A� 15� (1)� )� into� the� internal� address�

�counter� for� that� port.�

�Counter� Increment� Input.� Asserting� this� signal� LOW� (� CNTINC� =� V� IL� )�

�CNTINC� P1�

�CNTINC� P2�

�CNTINC� P3�

�CNTINC� P4�

�increments� the� internal� address� counter� for� that� port� on� each� rising� edge�

�of� the� clock� signal.� The� counter� will� increment� as� defined� by� the� counter�

�mask� register� for� that� port� (default� mode� is� to� advance� one� address� on�

�each� clock� cycle).�

�CNTRD� P1�

�CNTRD� P2�

�CNTRD� P3�

�CNTRD� P4�

�Counter� Readback� Input.� When� asserted� LOW� (� CNTRD� =� V� IL� )� causes� that�

�port� to� output� the� value� of� its� internal� address� counter� on� the� address�

�lines� for� that� port.� Counter� readback� is� independent� of� the� chip� enables�

�for� that� port.� If� the� port� is� activated� (� CE� 0� =� V� IL� and� CE� 1� =� V� IH� ),� during� the�

�counter� readback� operation,� then� the� data� bus� will� output� the� data�

�associated� with� that� readback� address� in� the� FourPort� memory� array�

�(assuming� that� the� byte� enables� and� output� enables� are� also� asserted).�

�Truth� Table� III� indicates� the� required� states� for� all� other� counter� controls�

�during� this� operation.� The� specific� operation� and� timing� of� this� funcion� is�

�described� in� detail� in� the� text.�

�CNTRST� P1�

�CNTRST� P2�

�CNTRST� P3�

�CNTRST� P4�

�Counter� Reset� Input.� Asserting� this� signal� LOW� (� CNTRST� =� V� IL� )� resets�

�the� address� counter� for� that� port� to� zero.�

�CNTINT� P1�

�CNTINT� P2�

�CNTINT� P3�

�CNTINT� P4�

�Counter� Interrupt� Flag� Output� .� This� signal� is� asserted� LOW� (� CNTINT� =�

�V� IL� )� when� the� internal� address� counter� for� that� port� 'wraps� around'� from�

�max� address� [(the� counter� will� increment� as� defined� by� the� counter� mask�

�register� for� that� port� (default� mode� is� to� advance� one� address� on� each�

�clock� cycle)]� to� address� min.� as� the� result� of� counter� increment� (� CNTINT�

�=� V� IL� ).� The� signal� goes� LOW� for� one� clock� cycle,� then� automatically�

�resets.�

�5649� tbl� 01�

�5�

�6.42�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT70V631S10PRFG | IC SRAM 4MBIT 10NS 128TQFP |

| IDT70V639S12PRFI | IC SRAM 2.25MBIT 12NS 128TQFP |

| IDT70V659S12DRI | IC SRAM 4MBIT 12NS 208QFP |

| IDT70V7319S166BCI | IC SRAM 4MBIT 166MHZ 256BGA |

| IDT70V7339S166BCI | IC SRAM 9MBIT 166MHZ 256BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V5388S166BGI8 | 功能描述:IC SRAM 1.125MBIT 166MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5388S200BC | 功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5388S200BC8 | 功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5388S200BCG | 功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5388S200BG | 功能描述:IC SRAM 1.125MBIT 200MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。