- 您现在的位置:买卖IC网 > PDF目录9968 > IDT72V3654L15PF (IDT, Integrated Device Technology Inc)IC BI FIFO 4096X36 15NS 128QFP PDF资料下载

参数资料

| 型号: | IDT72V3654L15PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 33/37页 |

| 文件大小: | 0K |

| 描述: | IC BI FIFO 4096X36 15NS 128QFP |

| 标准包装: | 36 |

| 系列: | 72V |

| 功能: | 异步 |

| 存储容量: | 147K(4K x 36) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 72V3654L15PF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页

5

COMMERCIALTEMPERATURERANGE

IDT72V3654/72V3664/72V3674 3.3V CMOS SyncBiFIFOTM WITH BUS-MATCHING

2,048 x 36 x 2, 4,096 x 36 x 2 and 8,192 x 36 x 2

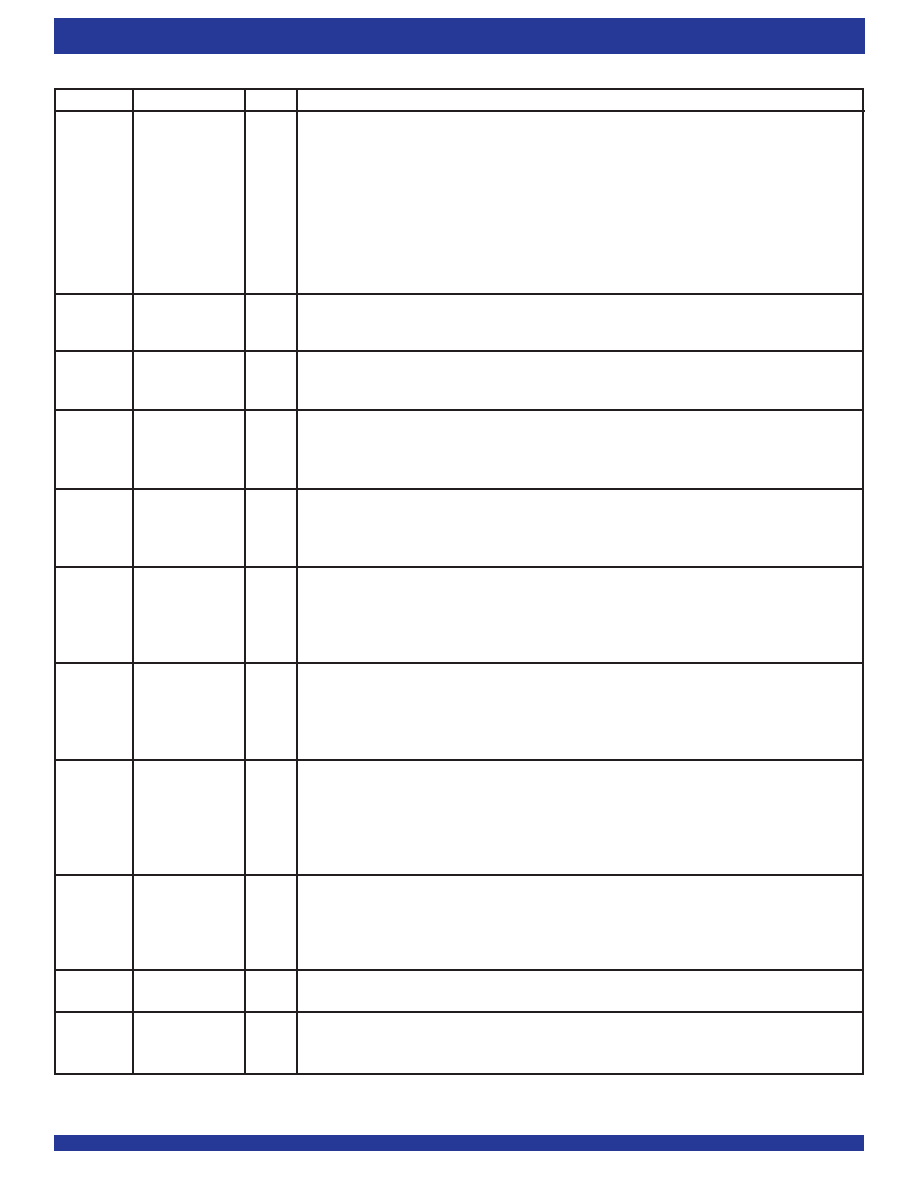

Symbol

Name

I/O

Description

FS0/SD

Flag Offset Select 0/

I

FS1/

SENand FS0/SD are dual-purpose inputs used for flag offset register programming. During

Serial Data

Master Reset, FS1/

SENandFS0/SD,togetherwithFS2,selecttheflagoffsetprogrammingmethod

Three offset register programming methods are available: automatically load one of five preset values

(8, 16, 64, 256 or 1,024), parallel load from Port A, and serial load.

FS1/

SEN

Flag Offset Select 1/

I

Serial Enable,

When serial load is selected for flag offset register programming, FS1/

SENis used as an enable

synchronous to the LOW-to-HIGH transition of CLKA. When FS1/

SENis LOW, a rising edge on CLKA

FS2(1)

Flag Offset Select 2

I

load the bit present on FS0/SD into the X and Y registers. The number of bit writes required to program

the offset registers is 44 for the IDT72V3654, 48 for the IDT72V3664, and 52 for the IDT72V3674.

The first bit write stores the Y-register (Y1) MSB and the last bit write stores the X-register (X2) LSB.

MBA

Port A Mailbox

I

A HIGH level on MBA chooses a mailbox register for a Port A read or write operation. When

Select

the A0-A35 outputs are active, a HIGH level on MBA selects data from the mail2 register for output

and a LOW level selects FIFO2 output register data for output.

MBB

Port B Mailbox

I

A HIGH level on MBB chooses a mailbox register for a Port B read or write operation. When the

Select

B0-B35 outputs are active, a HIGH level on MBB selects data from the mail1 register for output and

a LOW level selects FIFO1 output register data for output.

MBF1

Mail1 Register

O

MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to the mail1 register.

Flag

Writes to the mail1 register are inhibited while

MBF1is LOW. MBF1is set HIGH by a LOW-to-HIGH

transition of CLKB when a Port B read is selected and MBB is HIGH.

MBF1 is set HIGH following either

a Master or Partial Reset of FIFO1.

MBF2

Mail2 Register

O

MBF2is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the mail2 register. Writes

Flag

to the mail2 register are inhibited while

MBF2is LOW. MBF2is set HIGH by a LOW-to-HIGH

transition of CLKA when a Port A read is selected and MBA is HIGH.

MBF2 is set HIGH following

either a Master or Partial Reset of FIFO2.

MRS1

FIFO1 Master

I

A LOW on this pin initializes the FIFO1 read and write pointers to the first location of memory and sets the

Reset

Port B output register to all zeroes. A LOW-to-HIGH transition on

MRS1 selects the programming

method (serial or parallel) and one of five programmable flag default offsets for FIFO1 and FIFO2. It

also configures Port B for bus size and endian arrangement. Four LOW-to-HIGH transitions of CLKA

and four LOW-to-HIGH transitions of CLKB must occur while

MRS1is LOW.

MRS2

FIFO2 Master

I

A LOW on this pin initializes the FIFO2 read and write pointers to the first location of memory and sets

Reset

the Port A output register to all zeroes. A LOW-to-HIGH transition on

MRS2, toggled simultaneously with

MRS1, selects the programming method (serial or parallel) and one of the programmable flag default

offsets for FIFO2. Four LOW-to-HIGH transitions of CLKA and four LOW-to-HIGH transitions of CLKB

must occur while

MRS2is LOW.

PRS1/

PartialReset/

I

This pin is muxed for both Partial Reset and Retransmit operations, it is used in conjunction with the RTM

RT1

RetransmitFIFO1

pin. If RTM is in a LOW condition, a LOW on this pin performs a Partial Reset on FIFO1 and initializes

the FIFO1 read and write pointers to the first location of memory and sets the Port B output register to

all zeroes. During Partial Reset, the currently selected bus size, endian arrangement, programming

method (serial or parallel), and programmable flag settings are all retained. If RTM is HIGH, a LOW on

this pin performs a Retransmit and initializes the FIFO1 read pointer only to the first memory location.

PRS2/

PartialReset/

I

This pin is muxed for both Partial Reset and Retransmit operations, it is used in conjunction with the RTM

RT2

RetransmitFIFO2

pin. If RTM is in a LOW condition, a LOW on this pin performs a Partial Reset on FIFO2 and initializes

the FIFO2 read and write selected bus size, endian arrangement, programming method (serial or

parallel), and programmable flag settings are all retained. If RTM is HIGH, a LOW on this pin performs

a Retransmit and initializes the FIFO2 read pointer only to the first memory location.

RTM

RetransmitMode

I

This pin is used in conjunction with the

RT1 and RT2 pins. When RTM is HIGH a Retransmit is performed

on FIFO1 or FIFO2 respectively.

SIZE(1)

Bus Size Select

I

A HIGH on this pin when BM is HIGH selects byte bus (9-bit) size on Port B. A LOW on this pin when

BM is HIGH selects word (18-bit) bus size. SIZE works with BM and BE to select the bus size and endian

arrangement for Port B. The level of SIZE must be static throughout device operation

PIN DESCRIPTIONS (CONTINUED)

NOTE:

1. FS2, BM and SIZE inputs are not TTL compatible. These inputs should be tied to GND or VCC.

相关PDF资料 |

PDF描述 |

|---|---|

| V48B12M250BL3 | CONVERTER MOD DC/DC 12V 250W |

| V48B12M250BL | CONVERTER MOD DC/DC 12V 250W |

| IDT72V3653L15PF | IC SYNCFIFO 2048X36 15NS 128TQFP |

| IDT82P2521BH | IC LIU E1 21+1CH SHORT 640-PBGA |

| IDT72V3652L15PQF | IC BI FIFO 4096X36 15NS 132QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3654L15PF8 | 功能描述:IC BI FIFO 4096X36 15NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PF | 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PF8 | 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PFI | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

| IDT72V3656L10PFI8 | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

发布紧急采购,3分钟左右您将得到回复。