- 您现在的位置:买卖IC网 > PDF目录9968 > IDT72V3654L15PF (IDT, Integrated Device Technology Inc)IC BI FIFO 4096X36 15NS 128QFP PDF资料下载

参数资料

| 型号: | IDT72V3654L15PF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 6/37页 |

| 文件大小: | 0K |

| 描述: | IC BI FIFO 4096X36 15NS 128QFP |

| 标准包装: | 36 |

| 系列: | 72V |

| 功能: | 异步 |

| 存储容量: | 147K(4K x 36) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-TQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 72V3654L15PF |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

14

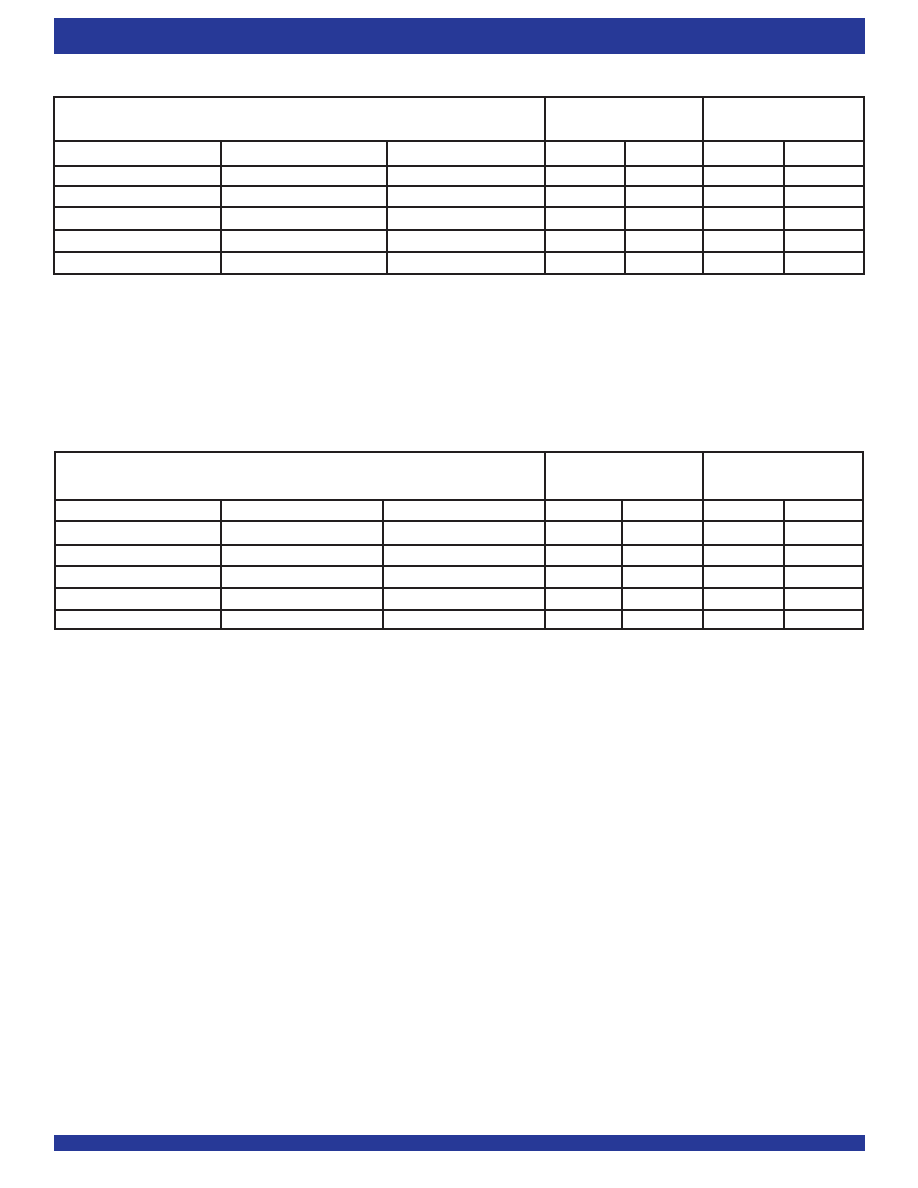

COMMERCIALTEMPERATURERANGE

IDT72V3654/72V3664/72V3674 3.3V CMOS SyncBiFIFOTM WITH BUS-MATCHING

2,048 x 36 x 2, 4,096 x 36 x 2 and 8,192 x 36 x 2

Synchronized

Number of Words in FIFO Memory(1,2)

to CLKA

to CLKB

IDT72V3654(3)

IDT72V3664(3)

IDT72V3674(3)

EFA/ORA

AEA

AFB

FFB/IRB

000

L

H

1 to X2

H

L

H

(X2+1) to [2,048-(Y2+1)]

(X2+1) to [4,096-(Y2+1)]

(X2+1) to [8,192-(Y2+1)]

H

(2,048-Y2) to 2,047

(4,096-Y2) to 4,095

(8,192-Y2) to 8,191

H

L

H

2,048

4,096

8,192

H

L

TABLE 4 — FIFO1 FLAG OPERATION (IDT Standard and FWFT modes)

TABLE 5 — FIFO2 FLAG OPERATION (IDT Standard and FWFT modes)

Synchronized

Number of Words in FIFO Memory(1,2)

to CLKB

to CLKA

IDT72V3654(3)

IDT72V3664(3)

IDT72V3674(3)

EFB/ORB

AEB

AFA

FFA/IRA

00

0

L

H

1 to X1

H

L

H

(X1+1) to [2,048-(Y1+1)]

(X1+1) to [4,096-(Y1+1)]

(X1+1) to [8,192-(Y1+1)]

H

(2,048-Y1) to 2,047

(4,096-Y1) to 4,095

(8,192-Y1) to 8,191

H

L

H

2,048

4,096

8,192

H

L

ENA is HIGH, MBA is LOW, and

EFA/ORA is HIGH (see Table 2). FIFO

reads and writes on Port A are independent of any concurrent Port B

operation.

The Port B control signals are identical to those of Port A with the

exception that the Port B Write/Read select (

W/RB) is the inverse of the Port

A Write/Read select (W/

RA). The state of the Port B data (B0-B35) lines is

controlled by the Port B Chip Select (

CSB) and Port B Write/Read select

(

W/RB). The B0-B35 lines are in the high-impedance state when either CSB

is HIGH or

W/RB is LOW. The B0-B35 lines are active outputs when CSB is

LOW and

W/RB is HIGH.

Data is loaded into FIFO2 from the B0-B35 inputs on a LOW-to-HIGH

transition of CLKB when

CSB is LOW, W/RB is LOW, ENB is HIGH, MBB is

LOW, and

FFB/IRB is HIGH. Data is read from FIFO1 to the B0-B35 outputs

byaLOW-to-HIGHtransitionofCLKBwhen

CSBisLOW,W/RBisHIGH,ENB

is HIGH, MBB is LOW, and

EFB/ORBisHIGH(seeTable3).FIFOreadsand

writes on Port B are independent of any concurrent Port A operation.

The setup and hold time constraints to the port clocks for the port Chip

SelectsandWrite/Readselectsareonlyforenablingwriteandreadoperations

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since in FWFT mode, the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X1 is the Almost-Empty offset for FIFO1 used by

AEB. Y1 is the Almost-Full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a FIFO1 reset or port A programming.

4. The ORB and IRA functions are active during FWFT mode; the

EFB and FFA functions are active in IDT Standard mode.

NOTES:

1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

2. Data in the output register does not count as a "word in FIFO memory". Since in FWFT mode, the first word written to an empty FIFO goes unrequested to the output register (no read

operation necessary), it is not included in the FIFO memory count.

3. X2 is the Almost-Empty offset for FIFO2 used by

AEA. Y2 is the Almost-Full offset for FIFO2 used by AFB. Both X2 and Y2 are selected during a FIFO2 reset or port A programming.

4. The ORA and IRB functions are active during FWFT mode; the

EFA and FFB functions are active in IDT Standard mode.

andarenotrelatedtohigh-impedancecontrolofthedataoutputs.Ifaportenable

is LOW during a clock cycle, the port’s Chip Select and Write/Read select may

change states during the setup and hold time window of the cycle.

WhenoperatingtheFIFOinFWFTmodeandtheOutputReadyflagisLOW,

the next word written is automatically sent to the FIFO’s output register by the

LOW-to-HIGHtransitionoftheportclockthatsetstheOutputReadyflagHIGH.

When the Output Ready flag is HIGH, subsequent data is clocked to the output

registers only when a read is selected using the port’s Chip Select, Write/Read

select, Enable, and Mailbox select.

When operating the FIFO in IDT Standard mode, the first word will cause

the Empty Flag to change state on the second LOW-to-HIGH transition of the

Read Clock. The data word will not be automatically sent to the output register.

Instead, data residing in the FIFO's memory array is clocked to the output

register only when a read is selected using the port’s Chip Select, Write/Read

select, Enable, and Mailbox select. Write and read timing diagrams for Port A

can be found in Figure 7 and 14. Relevant Port B write and read cycle timing

diagrams together with Bus-Matching and Endian select operations can be

found in Figures 8 through 13.

相关PDF资料 |

PDF描述 |

|---|---|

| V48B12M250BL3 | CONVERTER MOD DC/DC 12V 250W |

| V48B12M250BL | CONVERTER MOD DC/DC 12V 250W |

| IDT72V3653L15PF | IC SYNCFIFO 2048X36 15NS 128TQFP |

| IDT82P2521BH | IC LIU E1 21+1CH SHORT 640-PBGA |

| IDT72V3652L15PQF | IC BI FIFO 4096X36 15NS 132QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3654L15PF8 | 功能描述:IC BI FIFO 4096X36 15NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PF | 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PF8 | 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3656L10PFI | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

| IDT72V3656L10PFI8 | 制造商:Integrated Device Technology Inc 功能描述:IC SYNC FIFO 4096X36 10NS 128QFP |

发布紧急采购,3分钟左右您将得到回复。