- 您现在的位置:买卖IC网 > PDF目录9968 > IDT82V2088BB (IDT, Integrated Device Technology Inc)IC LIU T1/J1/E1 8CH 208-BGA PDF资料下载

参数资料

| 型号: | IDT82V2088BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 27/78页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/J1/E1 8CH 208-BGA |

| 标准包装: | 10 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BGA |

| 供应商设备封装: | 208-PBGA(17x17) |

| 包装: | 托盘 |

| 其它名称: | 82V2088BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页

33

INDUSTRIAL

TEMPERATURE RANGES

OCTAL CHANNEL T1/E1/J1 LONG HAUL/SHORT HAUL LINE INTERFACE UNIT

3.10 MCLK AND TCLK

3.10.1 MASTER CLOCK (MCLK)

MCLK is an independent, free-running reference clock. MCLK is 1.544

MHz or 37.056 MHz for T1/J1 applications and 2.048 MHz or 49.152 MHz

in E1 mode. This reference clock is used to generate several internal ref-

erence signals:

Timing reference for the integrated clock recovery unit.

Timing reference for the integrated digital jitter attenuator.

Timing reference for microcontroller interface.

Generation of RCLK signal during a loss of signal condition if AIS is

enabled.

Reference clock during a blue alarm Transmit All Ones (TAOS), all

zeros, PRBS/QRSS and inband loopback patterns if it is selected

as the reference clock. For ATAO and AIS, MCLK is always used as

the reference clock.

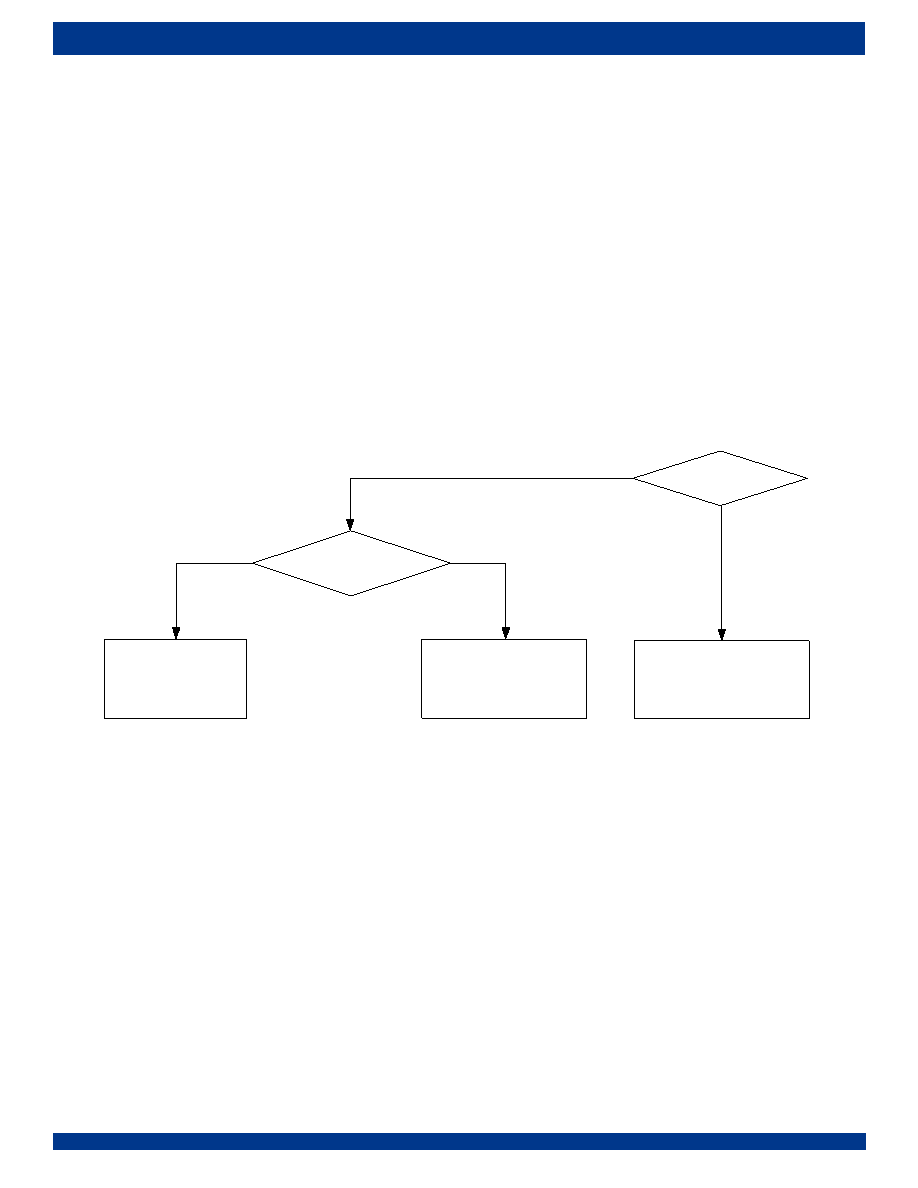

Figure-20 shows the chip operation status in different conditions of

MCLK and TCLKn. The missing of MCLK will set all the eight TTIP/TRING

to high impedance state.

3.10.2 TRANSMIT CLOCK (TCLK)

The TCLKn is used to sample the transmit data on TDn/TDPn, TDNn.

The active edge of TCLKn can be selected by the TCLK_SEL bit (TCF0,

02H...). During Transmit All Ones, PRBS/QRSS patterns or Inband Loop-

back Code,either TCLKnor MCLK can beused as the referenceclock. This

is selected by the PATT_CLK bit (MAINT0, 0AH...).

But for Automatic Transmit All Ones and AIS, only MCLK is used as the

reference clock and the PATT_CLK bit is ignored. In Automatic Transmit

All Ones condition, the ATAO bit (MAINT0, 0AH) is set to ‘1’. In AIS condi-

tion, the AISE bit (MAINT0, 0AH) is set to ‘1’.

If TCLKn has been missing for more than 70 MCLK cycles, TCLK_LOS

bit (STAT0, 14H...) will be set, and the corresponding TTIPn/TRINGn will

become high impedance if this channel is not used for remote loopback or

isnotusingMCLK totransmitinternal patterns (TAOS,AllZeros,PRBSand

in-band loopback code). When TCLKn is detected again, TCLK_LOS bit

(STAT0,14H...)willbecleared.ThereferencefrequencytodetectaTCLKn

loss is derived from MCLK.

Figure-20 TCLK Operation Flowchart

normal operation mode

transmitter n enters high

impedance status and

generates transmit clock loss

interrupt if not masked

TCLKn status?

clocked

L/H

MCLK=H/L?

all transmitters high

impedance status

yes

clocked

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V263L7-5PF | IC FIFO 8192X18 7-5NS 80QFP |

| V48B15M250BG2 | CONVERTER MOD DC/DC 15V 250W |

| IDT82V2088BBG | IC LINE INTERFACE UNIT 208-PBGA |

| V48B15M250BF3 | CONVERTER MOD DC/DC 15V 250W |

| IDT72V263L10PFI | IC FIFO 8192X18 10NS 80QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2088BBG | 功能描述:IC LINE INTERFACE UNIT 208-PBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2088DR | 功能描述:IC LIU T1/J1/E1 8CH 208-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2088DRG | 功能描述:IC LIU T1/J1/E1 8CH 208-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2108 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:T1 / E1 / J1 OCTAL FRAMER |

| IDT82V2108BB | 功能描述:IC FRAMER T1/J1/E1 8CH 144-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

发布紧急采购,3分钟左右您将得到回复。