- 您现在的位置:买卖IC网 > PDF目录1809 > IR3529MTRPBF (International Rectifier)IC CTRL XPHASE CPU/ASIC 20-MLPQ PDF资料下载

参数资料

| 型号: | IR3529MTRPBF |

| 厂商: | International Rectifier |

| 文件页数: | 13/22页 |

| 文件大小: | 0K |

| 描述: | IC CTRL XPHASE CPU/ASIC 20-MLPQ |

| 标准包装: | 1 |

| 系列: | XPhase3™ |

| 应用: | 处理器 |

| 电流 - 电源: | 2mA |

| 电源电压: | 8 V ~ 16 V |

| 工作温度: | 0°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-MLPQ |

| 供应商设备封装: | 20-MLPQ(4x4) |

| 包装: | 标准包装 |

| 其它名称: | IR3529MTRPBFDKR |

�� �

�

�

�IR3529�

�A� synchronous� rectification� disable� comparator� is� used� to� detect� the� converter’s� CSIN-� pin� voltage,� which�

�represents� local� converter� output� voltage.� If� the� voltage� is� below� 75%� of� VDAC� and� negative� current� is� detected,�

�GATEL� is� driven� low,� which� disables� synchronous� rectification� and� eliminates� negative� current� during� power-up.�

�The� gate� drivers� are� pulled� low� if� the� supply� voltage� falls� below� the� normal� operating� range.� An� 80k�

�resistor� is�

�connected� across� the� GATEH/GATEL� and� PGND� pins� to� prevent� the� GATEH/GATEL� voltage� from� rising� due� to�

�leakage� or� other� causes� under� these� conditions.�

�PWM� Ramp�

�Every� time� the� phase� IC� is� powered� up,� the� PWM� ramp� magnitude� is� calibrated� to� generate� a� 52.5� mV/%� ramp�

�(VCC=12V).� For� example,� a� 15� %� duty� ratio� will� generate� a� ramp� amplitude� of� 787.5� mV� (15� x� 52.5� mV)� with�

�12V� supply� applied� to� VCC.� Feed-forward� control� is� achieved� by� varying� the� PWM� ramp� proportionally� with� VCC�

�voltage� after� calibration.�

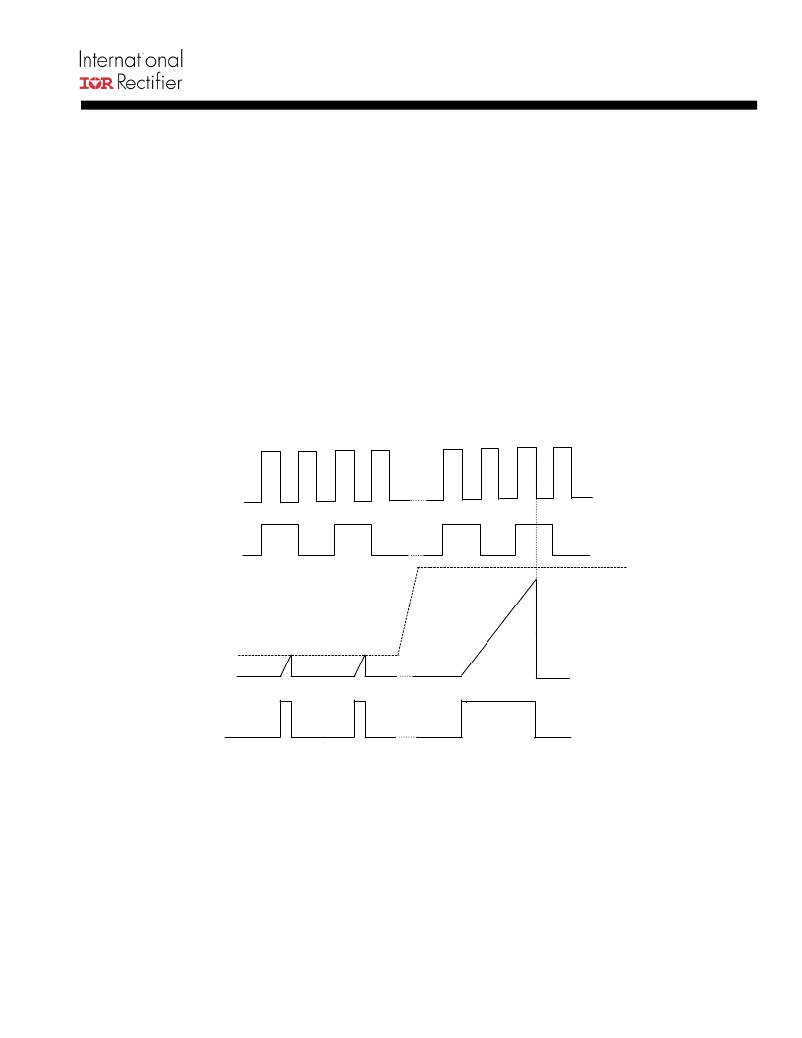

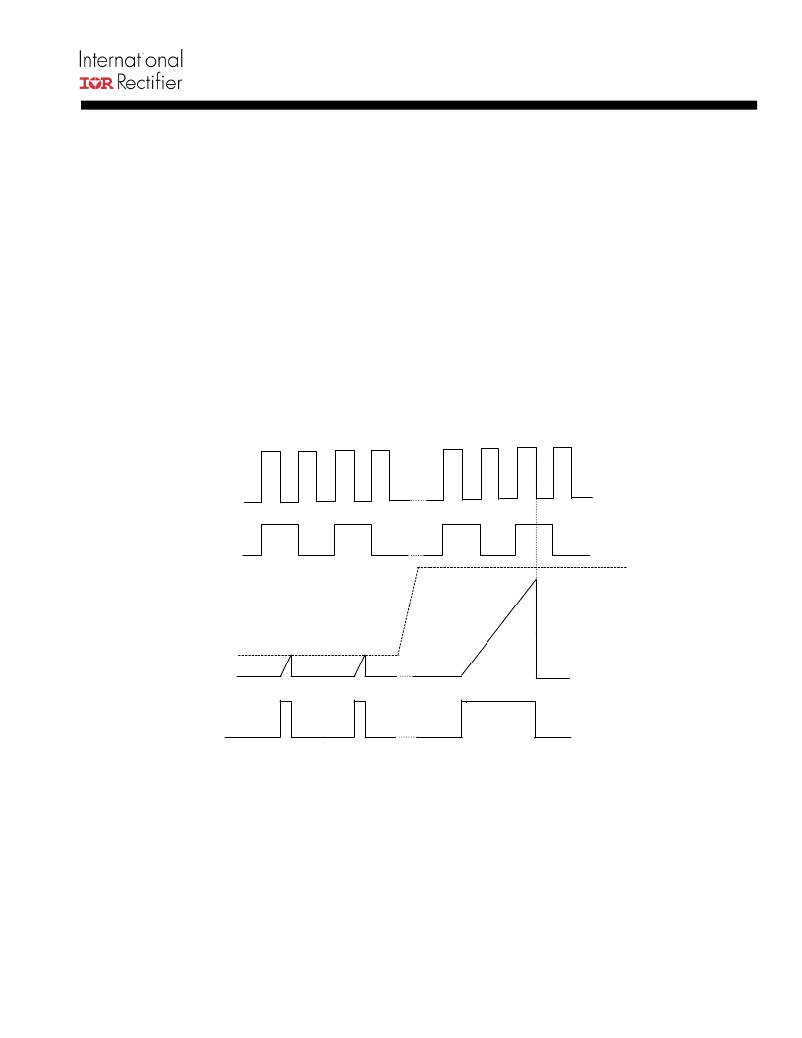

�In� response� to� a� load� step-up,� the� error� amplifier� can� demand� 100� %� duty� cycle.� As� shown� in� Figure� 6,� 100� %�

�duty� is� detected� by� comparing� the� PWM� latch� output� (PWMQ)� and� its� input� clock� (PWM_CLK).� If� the� PWMQ� is�

�high� when� the� PWM_CLK� is� asserted,� the� top� FET� turnoff� is� initiated.� The� top� FET� is� again� turned� on� once� the�

�RMPOUT� drops� within� 200� mV� of� the� VDAC.�

�NORMAL� OPERATION�

�100� %� DUTY� OPERATION�

�CLKIN�

�PHIN�

�(2� Phase� Design)�

�EAIN�

�RMPOUT�

�PWMQ�

�Figure� 6:� PWM� Operation� during� normal� and� 100� %� duty� mode.�

�Power� State� Indicator� (PSI)� function�

�From� a� system� perspective,� the� PSI� input� is� controlled� by� the� system� and� is� forced� low� when� the� load� current� is�

�lower� than� a� preset� limit� and� forced� high� when� load� current� is� higher� than� the� preset� limit.� IR3529� can� accept� an�

�active� low� signal� on� its� PSI� input� and� force� the� drivers� into� tri-state,� effectively,� forcing� the� phase� IC� into� an� off�

�state.� Once� the� PSI#� signal� is� asserted,� the� IC� waits� for� 8� PHSIN� cycles� before� forcing� the� drivers� into� tri-state.�

�This� delay� is� required� to� ensure� that� the� IC� does� not� respond� to� any� high� frequency� PSI#� signal� because�

�entering� into� PSI� mode� for� a� very� short� duration� does� not� benefit� the� system� efficiency.� Irrespective� of� the� PSI#�

�input,� the� disabled� phase� remains� connected� to� the� ILL� bus� which� ensures� accurate� voltage� positioning.�

�However,� on� assertion� of� PSI#� signal,� the� disabled� phase� is� disconnected� from� the� ISHARE� bus� and� therefore�

�ISHARE� will� represent� the� actual� per� phase� current� information.�

�Page� 13� of� 22�

�February� 12,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| IR3550MTRPBF | IC DRIVER GATE 60A PQFN |

| IR3553MTRPBF | IC DRIVER GATE 40A PQFN |

| IR3621FTR | IC REG CTRLR BUCK PWM VM 28TSSOP |

| IR3622AMPBF | IC REG CTRLR BUCK PWM VM 32MLPQ |

| IR3622MTRPBF | IC REG CTRLR BUCK PWM VM 32MLPQ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IR3531A | 制造商:IRF 制造商全称:International Rectifier 功能描述:41 Phase Dual Output Control IC Pre-bias compatible |

| IR3531A-MPBF | 制造商:IRF 制造商全称:International Rectifier 功能描述:41 Phase Dual Output Control IC Pre-bias compatible |

| IR3531AMTRPBF | 制造商:International Rectifier 功能描述:4+1 DUAL OUPUT CONTROLLER IC WITH I2C - Tape and Reel 制造商:International Rectifier 功能描述:IC OUTPUT CTRL 4+1 PHASE 48MLPQ 制造商:International Rectifier 功能描述:T&R / 4+1 Dual Ouput Controller IC with I2C |

| IR3531A-MTRPBF | 制造商:IRF 制造商全称:International Rectifier 功能描述:41 Phase Dual Output Control IC Pre-bias compatible |

| IR3531MTRPBF | 制造商:International Rectifier 功能描述:4+1 DUAL OUPUT CONTROLLER IC WITH I2C - Tape and Reel 制造商:International Rectifier 功能描述:IC OUTPUT CTRL 4+1 PHASE 48MLPQ 制造商:International Rectifier 功能描述:4 1 Dual Ouput Contr IC with I2C 制造商:International Rectifier 功能描述:T&R / 4+1 Dual Ouput Controller IC with I2C |

发布紧急采购,3分钟左右您将得到回复。