- 您现在的位置:买卖IC网 > PDF目录79629 > IS80C52CXXX-16:RD (ATMEL CORP) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 PDF资料下载

参数资料

| 型号: | IS80C52CXXX-16:RD |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 5/134页 |

| 文件大小: | 3805K |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页

102

8011Q–AVR–02/2013

ATmega164P/324P/644P

one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. This option is

not available for the OC0B pin (See Table 12-4 on page 105). The actual OC0x value will only

be visible on the port pin if the data direction for the port pin is set as output. The PWM wave-

form is generated by clearing (or setting) the OC0x Register at the Compare Match between

OCR0x and TCNT0 when the counter increments, and setting (or clearing) the OC0x Register at

Compare Match between OCR0x and TCNT0 when the counter decrements. The PWM fre-

quency for the output when using phase correct PWM can be calculated by the following

equation:

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A Register represent special cases when generating a PWM

waveform output in the phase correct PWM mode. If the OCR0A is set equal to BOTTOM, the

output will be continuously low and if set equal to MAX the output will be continuously high for

non-inverted PWM mode. For inverted PWM the output will have the opposite logic values.

At the very start of period 2 in Figure 12-7 OCnx has a transition from high to low even though

there is no Compare Match. The point of this transition is to guarantee symmetry around BOT-

TOM. There are two cases that give a transition without Compare Match.

OCR0A changes its value from MAX, like in Figure 12-7. When the OCR0A value is MAX the

OCn pin value is the same as the result of a down-counting Compare Match. To ensure

symmetry around BOTTOM the OCn value at MAX must correspond to the result of an up-

counting Compare Match.

The timer starts counting from a value higher than the one in OCR0A, and for that reason

misses the Compare Match and hence the OCn change that would have happened on the way

up.

12.8

Timer/Counter Timing Diagrams

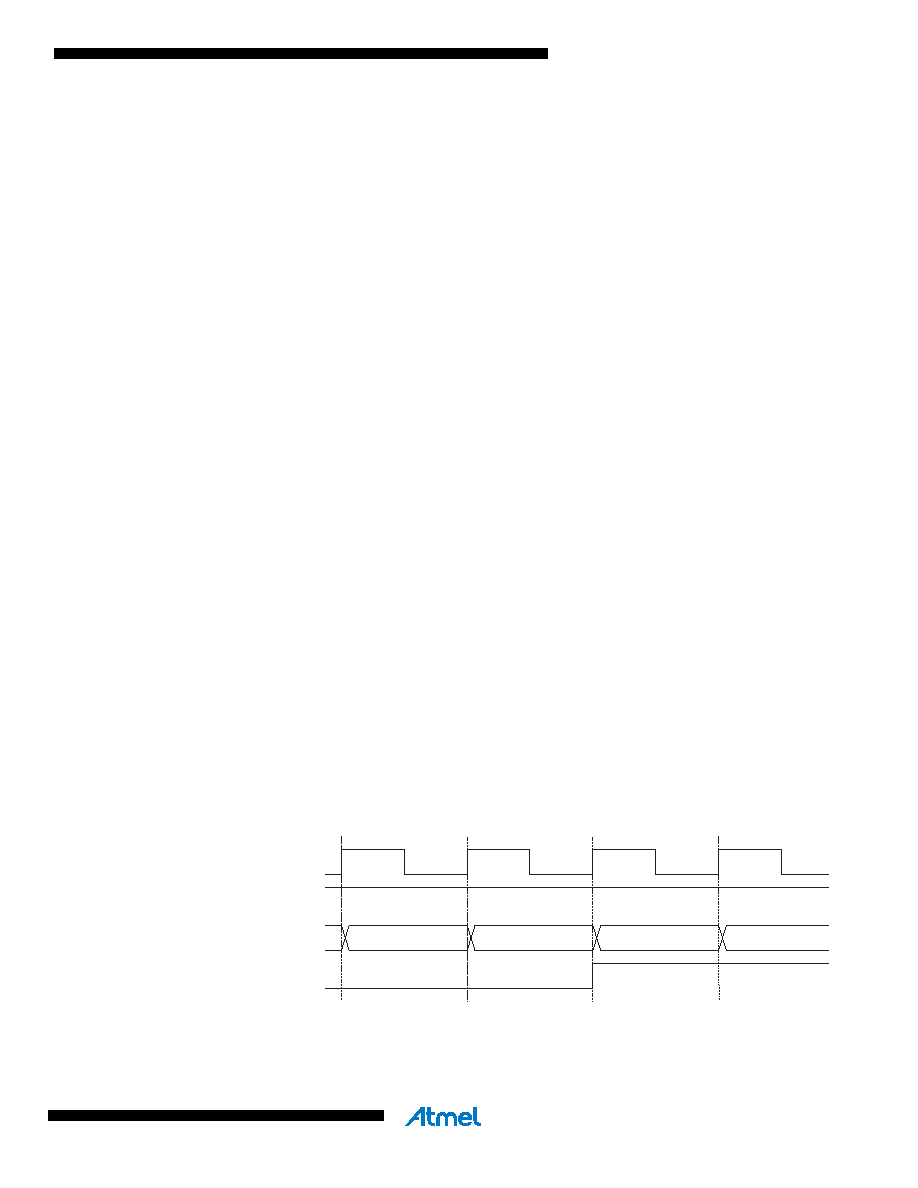

The Timer/Counter is a synchronous design and the timer clock (clk

T0) is therefore shown as a

clock enable signal in the following figures. The figures include information on when Interrupt

Flags are set. Figure 12-8 contains timing data for basic Timer/Counter operation. The figure

shows the count sequence close to the MAX value in all modes other than phase correct PWM

mode.

Figure 12-8. Timer/Counter Timing Diagram, no Prescaling

Figure 12-9 shows the same timing data, but with the prescaler enabled.

f

OCnxPCPWM

f

clk_I/O

N 510

------------------

=

clk

Tn

(clk

I/O/1)

TOVn

clk

I/O

TCNTn

MAX - 1

MAX

BOTTOM

BOTTOM + 1

相关PDF资料 |

PDF描述 |

|---|---|

| IS80C52CXXX-16SHXXX:R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| IS80C52CXXX-25:D | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQCC44 |

| IS80C52CXXX-30SHXXX:RD | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQCC44 |

| IS80C52CXXX-30SHXXX:R | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQCC44 |

| IS80C52CXXX-L16:R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS80C86 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IS80C86-2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IS80C86-2R2490 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IS80C88 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IS80C88-2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。