参数资料

| 型号: | ISL35822LPIK |

| 厂商: | Intersil |

| 文件页数: | 3/75页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 192EBGA-B |

| 标准包装: | 90 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 无 |

| 输入: | CML |

| 输出: | CML,CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 8:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.59Gbps |

| 电源电压: | 1.3 V ~ 1.41 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 192-EBGA |

| 供应商设备封装: | 192-EBGA-B(17x17) |

| 包装: | 托盘 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

11

data is detected in all four lanes within the span of the

Alignment FIFO, the deskewing (lane to lane) alignment

operation is performed, and will be held until another ||A|| or

IDLE-to- non-IDLE transition is detected again on the lanes.

During this alignment, up to four code groups may be

deleted on any lane. For correct operation, the XAUI Lane 0

signals should be connected to the ISL35822 Lane 0 pins.

The deskew algorithm state machines (each implemented

according to IEEE 802.3ae) are enabled by setting the

DSKW_SM_EN bits (Address [3,4].C000’h, see Table 63

and/or Table 80) to 1 or overriding them with the respective

XAUI_EN bits in the [3,4].C001’h registers (Table 64 and

Table 81). Note that when one side’s DSKW_SM_EN is set

to 1, the same side CAL_EN bit (Address [3,4].C000’h,

Table 63/Table 80) is ignored. When a DSKW_SM_EN bit is

set to 0, lane deskew can still be enabled by setting

CAL_EN, but the deskew action will be carried out without

hysteresis.

The user has the option to disable trunking, or to enable

trunking across each set of 4 lanes, in the PCS (device 3)

and PHY XGXS (device 4), under control of the respective

PSYNC bits in registers [3,4].C000h. In trunking mode, the

lanes may have phase differences, but they are expected to

be frequency synchronous. In non-trunking mode, each

received serial stream need only be within ±100ppm of the

nominal bit rate (2.488Gbps to 3.1875Gbps in full-speed

mode or 1.244Gbps to 1.59375Gbps in half-speed mode).

Setting the PSYNC bits high will enable the trunking mode,

so that all transmitted data will be synchronized to the same

clock. Note that trunking mode is only possible if 8B/10B

Coding is activated, and all lanes have the same half-rate

setting (See Table 71).

Clock Compensation

In addition to deskew, the Receive FIFOs also compensate

for clock differences. Since the received serial streams can,

under worst case conditions, be off by up to ±200ppm from

the local clock domain, the received data must be adjusted

to the local reference clock frequency.

Another 8 bytes of RXFIFO are dedicated for clock

compensation. The FIFOs achieve clock tolerance by

identifying any of the IDLE patterns (/K/, /A/ or /R/ as defined

by the IEEE 802.3ae standard) in the received data and then

adding or dropping IDLEs as needed. The Receive FIFO

does not store the actual IDLE sequences received but

generates the number of IDLEs needed to compensate for

clock tolerance differences. The IDLE patterns retransmitted

will be determined according to the IEEE 802.3ae algorithm

if the appropriate AKR_SM_EN bit is set in Registers

Transmitter Operations

8b/10b Encoding

The internal 10b encoding specified in the IEEE802.3-2002

specification, section 36.2.4 in Tables 36-1 & 36-2, and

discussed in more detail in “8b/10b Coding and Decoding”

page 12, is enabled by default in the PCS and PHY XS

through the setting of the respective CODECENA bits to 1’b,

and may be disabled through the MDIO registers

respective bit to 0’b. Note that the receive decoding will also

be disabled. The (decoded, synchronized and aligned) data

is transferred via the transmit FIFOs, (normally) encoded,

serialized and re-transmitted on the Serial Output pins,

whose effective output impedance is nominally 100

differential.

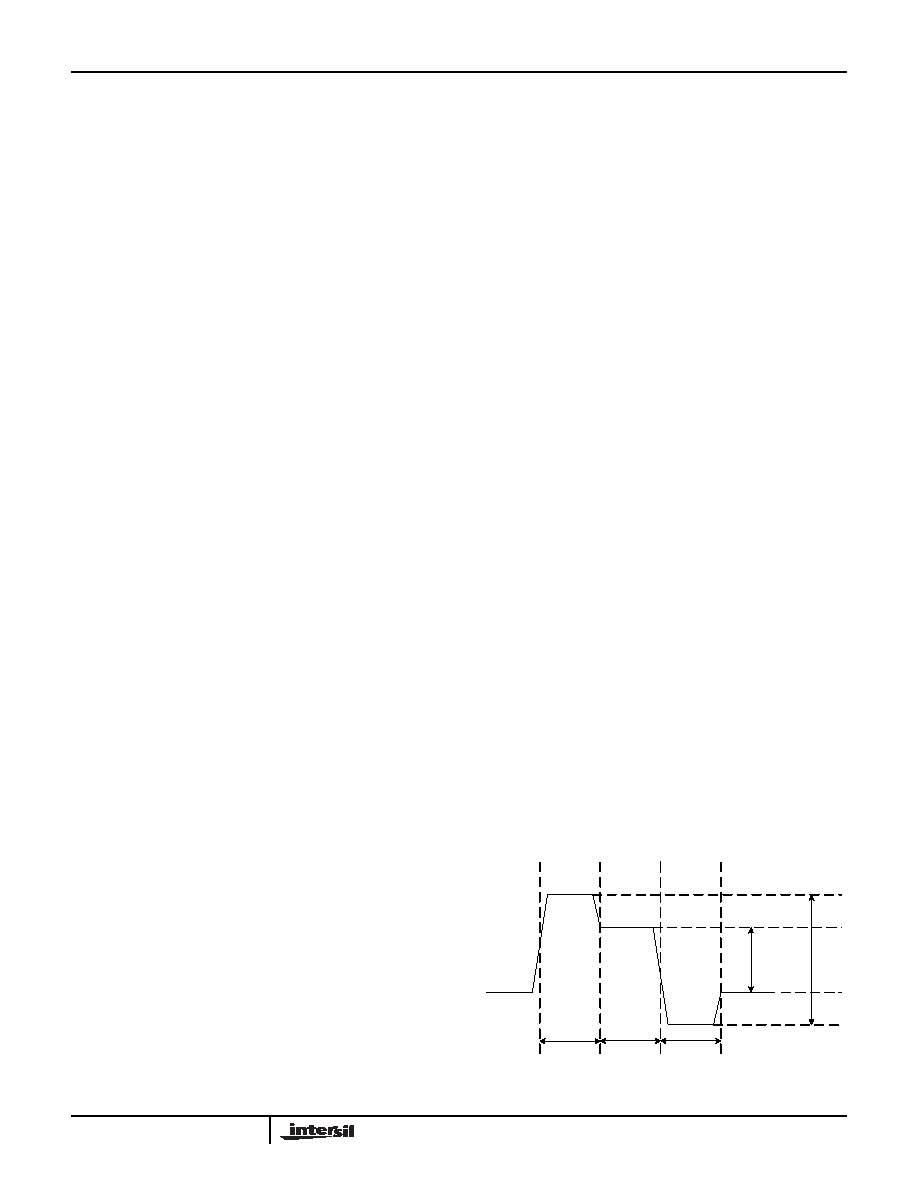

Pre-Emphasis

In order to compensate for the loss of the high frequency

signal component through PCB traces or the CX4 Cable

Assembly, sixteen levels of programmable pre-emphasis

have been provided on the CX4/LX4 PMA serial transmit

lanes, and eight levels on the XAUI PHY XS serial transmit

lanes. The output signal is boosted immediately after any

transition (see Figure 3). This maximizes the data eye

opening at the receiver inputs and enhances the bit error

rate performance of the system. The MDIO Registers at

the level of pre-emphasis for the PMA/PMD (sixteen levels)

and PHY XGXS (eight levels) respectively, settable from

none to the maximum. The initial default values of the

PMA/PMD register depend on the LX4_MODE configuration

pin, and are set to the optimum values for CX4 or XAUI

(assumed best for LX4 drivers). The PMA side has an

additional set of Pre-emphasis enabling bits, in 1.C00B.5:2

that enable or disable the predriver/pre-emphasis. In LX4

mode these default to disabled, to reduce the power

consumption. All these three registers may be auto-loaded

(see Auto-Configuring Control Registers page 16) from an

NVR EEPROM on start-up or RESET.

V

HI-pp

V

LOW-pp

Bit

Time

Bit

Time

Bit

Time

1

00

FIGURE 3. PRE-EMPHASIS OUTPUT ILLUSTRATION

ISL35822

相关PDF资料 |

PDF描述 |

|---|---|

| ISL41334IRZ-T7A | IC TXRX RS232/485 DL 2PRT 40QFN |

| ISL43485IB-T | IC TXRX 1TX/1RX 3V RS-485 8-SOIC |

| ISL51002CQZ-110 | IC FRONT END 10BIT VID 128-MQFP |

| ISL5314IN | IC SYNTHESIZER DIGITAL 48-MQFP |

| ISL55100AIRZ-T | IC COMP DRVR/WINDOW 18V 72-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL36111 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11.1Gb/s Lane Extender |

| ISL36111DRZ-EVALZ | 功能描述:EVAL BOARD FOR ISL36111DRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| ISL36111DRZ-T7 | 功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| ISL36111DRZ-TS | 功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| ISL36356A-APDK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PRISM 11Mbps Wireless Local Area Network Access Point |

发布紧急采购,3分钟左右您将得到回复。