参数资料

| 型号: | ISL35822LPIK |

| 厂商: | Intersil |

| 文件页数: | 37/75页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 192EBGA-B |

| 标准包装: | 90 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 无 |

| 输入: | CML |

| 输出: | CML,CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 8:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.59Gbps |

| 电源电压: | 1.3 V ~ 1.41 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 192-EBGA |

| 供应商设备封装: | 192-EBGA-B(17x17) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

42

Note (1): These values may be overwritten by the Auto-Configure operation (See “Auto-Configuring Control Registers” on page 16 and Table 92 for details).

Note (2): PCS loopback via bit 3.0.14 (Table 57) is NOT permitted by IEEE 802.3ae-2002 for 10GBASE-X PCS devices. Many XENPAK hosts, however, expect this

loopback (which is mandatory for 10GBASE-R PCS devices). Setting this bit will enable this loopback, but cause the ISL35822 to be non-conforming to the

current 802.3 specification. See “Loopback Modes ” on page 13).

Note (3): These bits are overridden by PCS XAUI_EN, see also Table 65.

Note (4): This state machine is implemented according to IEEE 802.3ae-2002 clause 48.2.6.

Note (1): “D” is either 3 for PCS or 4 for PHY XS. Behavior of the two devices is entirely independent of each other.

Note (1): The value may be overwritten by the Auto-Configure operation (See “Auto-Configuring Control Registers” on page 16 and Table 92 for details).

Note (1): The value may be overwritten by the Auto-Configure operation (See “Auto-Configuring Control Registers” on page 16 and Table 92 for details).

3.49153.6

PCS AKR_SM_EN

1 = enable random

A/K/R

0 = /K/ only(3)

0’b(1)

R/W

Enable pseudo- random A/K/R(4) in Inter Packet Gap

(IPG) on PCS transmitter side (vs. /K/ only)

3.49153.5

PCS TRANS_EN

1 = enable

0 = disable(3)

Overridden by

XAUI_EN, see

0’b(1)

R/W

This bit enables the transceiver to translate an “IDLE”

pattern in the internal FIFOs (matching the value of

register 3.C003’h) to and from the XAUI IDLE /K/

comma character or /A/, /K/ & /R/ characters.

3.49153.4

Reserved

3.49153.3

TX_SDR

PCS receive

data rate

0’b(1)

R/W

1 = PCS egress takes data from PHY XS at half speed

0 = PCS egress takes data from PHY XS at full speed

3.49153.2:0

Reserved

001’b

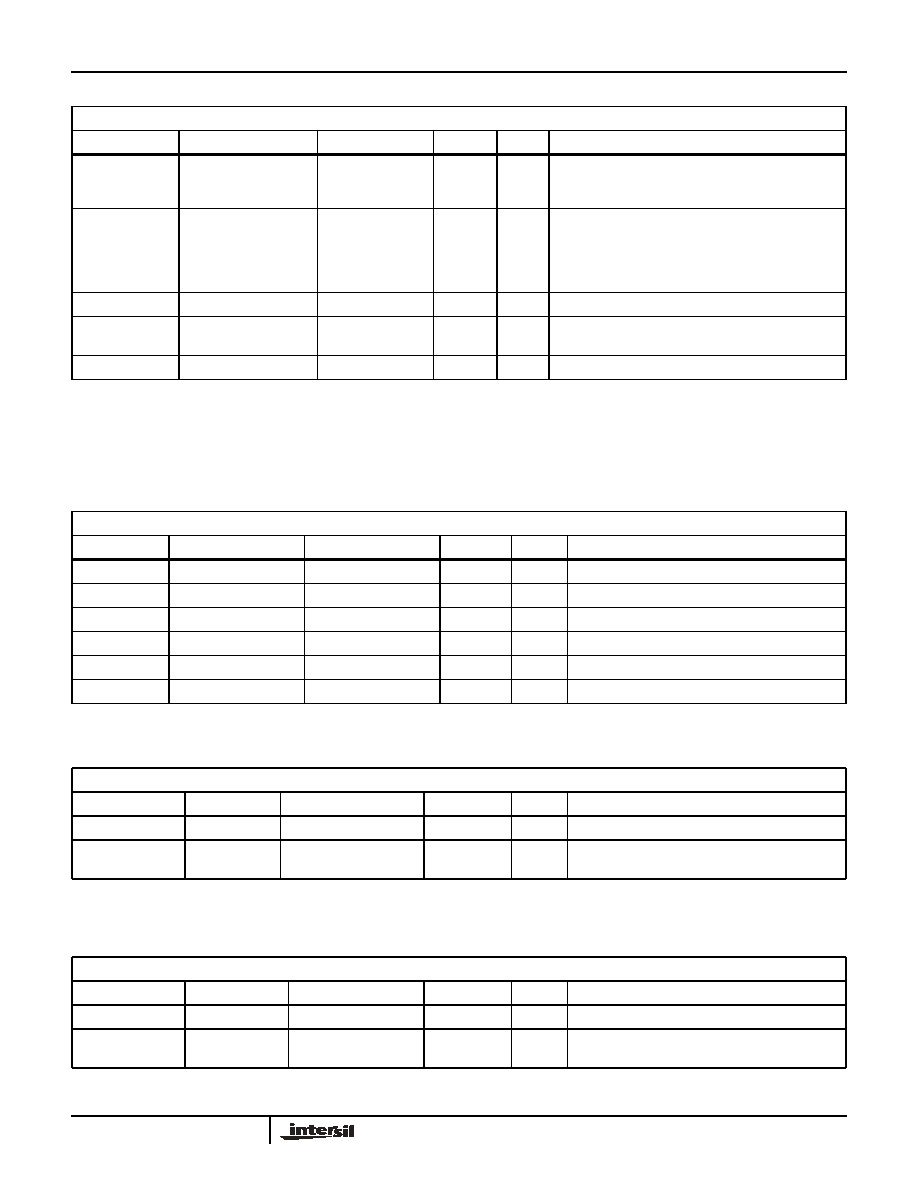

Table 64. PCS CONTROL REGISTER 3 (Continued)

MDIO REGISTER ADDRESS = 3.49153 (3.C001’h)

BIT

NAME

SETTING

DEFAULT

R/W

DESCRIPTION

Table 65. PCS or PHY XS XAUI_EN CONTROL OVERRIDE FUNCTIONS

BITS OVERRIDDEN BY XAUI_EN Bit, D.49153.11 (D.C001’h.11) = 1’b (1)

REG. BIT(1)

NAME

OVERRIDE TO

DEFAULT

R/W

DESCRIPTION

D.49153.5

TRANS_EN

1 = enable

0’b

R/W

Translates /A/K/R/ to-from /I/

D.49153.6

AKR_SM_EN

1 = enable

0’b

R/W

Generate pseudo-random /A/K/R/

D.49152.1

A_ALIGN_DIS

0 = enabled

1’b

R/W

Aligns data on incoming “||A||”

D.49152.4

PCS_SYNC_EN

1 = enable

0’b

R/W

IEEE Clause 48.2.6 State Machine

D.49152.7

DSKW_SM_EN

1 = enable

0’b

R/W

IEEE Clause 48.2.6 State Machine

D.49154

ERROR Code

FE’h

R/W

Internal FIFO ERROR character

Table 66. PCS INTERNAL ERROR CODE REGISTER

MDIO REGISTER, ADDRESS = 3.49154 (3.C002’h)

BIT

NAME

SETTING

DEFAULT(1)

R/W

DESCRIPTION

3.49154.15:8

Reserved

3.49154.7:0

PCS ERROR

Desired Value(2)

FE’h

R/W

Error Code. These bits allow the internal FIFO

ERROR control character to be programmed.

Table 67. PCS INTERNAL IDLE CODE REGISTER

MDIO REGISTER ADDRESS = 3.49155 (3.C003’h)

BIT

NAME

SETTING

DEFAULT(1)

R/W

DESCRIPTION

3.49155.15:8

Reserved

3.49155.7:0

PCS XG_IDLE

Desired Value

07’h

R/W

IDLE pattern in internal FIFOs for translation

to/from XAUI IDLEs

ISL35822

相关PDF资料 |

PDF描述 |

|---|---|

| ISL41334IRZ-T7A | IC TXRX RS232/485 DL 2PRT 40QFN |

| ISL43485IB-T | IC TXRX 1TX/1RX 3V RS-485 8-SOIC |

| ISL51002CQZ-110 | IC FRONT END 10BIT VID 128-MQFP |

| ISL5314IN | IC SYNTHESIZER DIGITAL 48-MQFP |

| ISL55100AIRZ-T | IC COMP DRVR/WINDOW 18V 72-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL36111 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11.1Gb/s Lane Extender |

| ISL36111DRZ-EVALZ | 功能描述:EVAL BOARD FOR ISL36111DRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| ISL36111DRZ-T7 | 功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| ISL36111DRZ-TS | 功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| ISL36356A-APDK | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PRISM 11Mbps Wireless Local Area Network Access Point |

发布紧急采购,3分钟左右您将得到回复。