参数资料

| 型号: | ISL6327AIRZ |

| 厂商: | Intersil |

| 文件页数: | 19/29页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM 48-QFN |

| 标准包装: | 43 |

| PWM 型: | 控制器 |

| 输出数: | 6 |

| 频率 - 最大: | 1MHz |

| 电源电压: | 4.75 V ~ 5.25 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

�� �

�

�

�ISL6327A�

�Soft-Start�

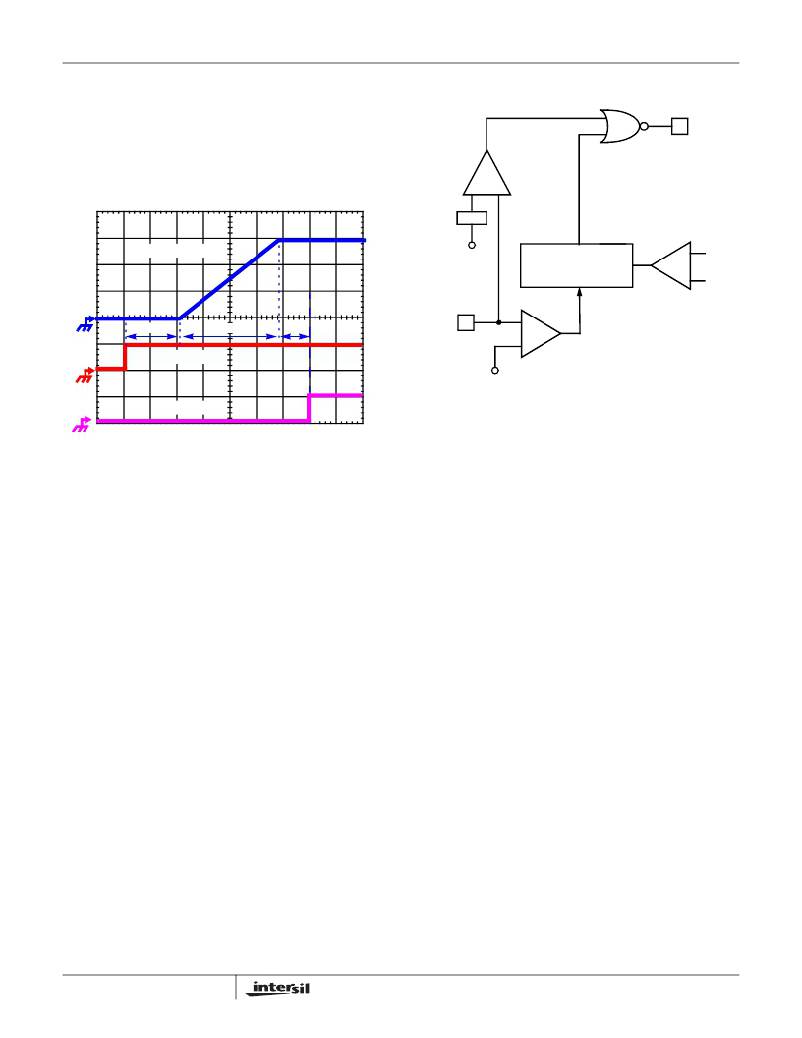

�The� soft-start� sequence� of� an� ISL6327A� based� VR� is�

�comprised� of� 3� segments,� as� shown� in� Figure� 8.� Once� VCC,�

�EN_VTT� and� EN_PWR� all� reach� their� POR/enable�

�thresholds,� the� controller� initiates� a� fixed� wait� period,� t� D1� .�

�Following� t� D1� ,� the� VR� initiates� the� soft-start� ramp,� raising� the�

�internal� reference� to� the� VID� setpoint� over� the� time� interval,�

�detected,� or� the� controller� is� disabled� by� a� reset� from�

�EN_PWR,� EN_VTT,� POR,� or� VID� OFF-code.�

�VR_RDY�

�UV�

�t� D2� .�

�50%�

�VOUT,� 500mV/DIV�

�DAC�

�SOFT-START,� FAULT�

�AND� CONTROL� LOGIC�

�-�

�OC�

�+�

�85μA�

�I� AVG�

�tD1�

�t� D2�

�t� D3�

�VDIFF�

�+�

�OV�

�-�

�EN_VTT�

�VID� +� 0.175V�

�VR_RDY�

�500μs/DIV�

�FIGURE� 8.� SOFT-START� WAVEFORMS�

�t� D1� is� a� fixed� delay� with� the� typical� value� as� 1.36ms.� During�

�t� D2� ,� ISL6327A� digitally� controls� the� DAC� voltage� change� at�

�6.25mV� per� step.� The� time� for� each� step� is� determined� by�

�the� frequency� of� the� soft-start� oscillator� which� is� defined� by�

�the� resistor� R� SS� from� SS� pin� to� GND.� The� soft-start� ramp�

�time� t� D2� can� be� calculated� based� on� Equations� 14:�

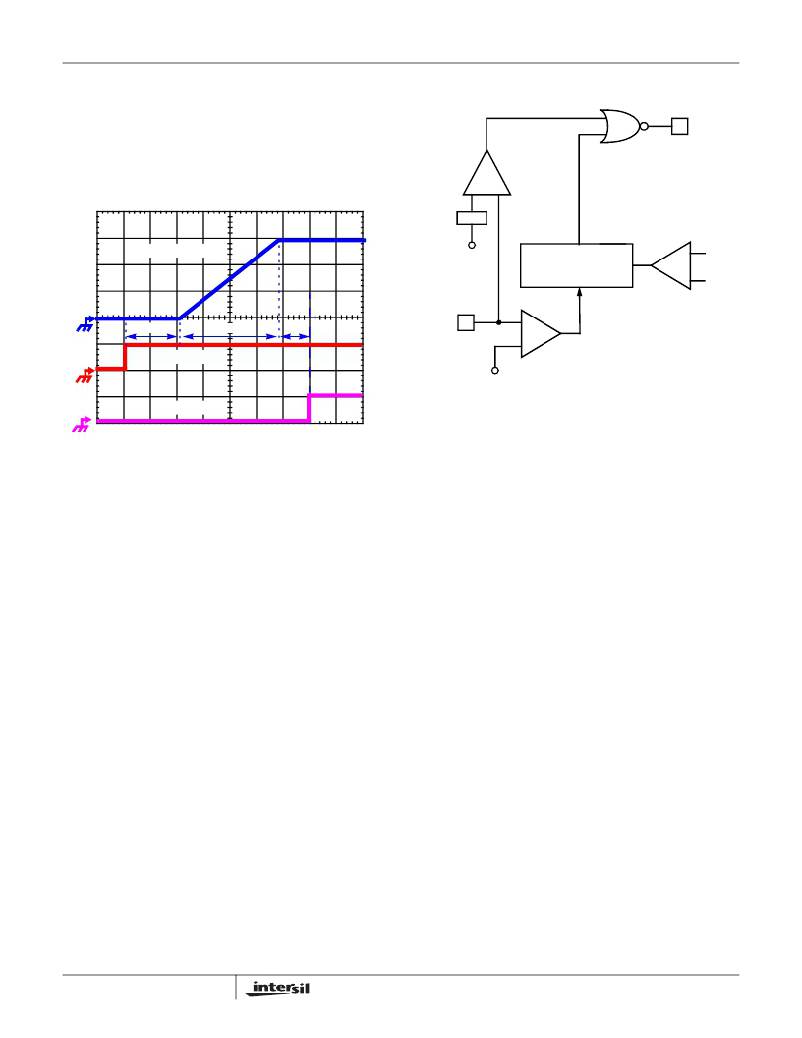

�FIGURE� 9.� VR_RDY� AND� PROTECTION� CIRCUITRY�

�Undervoltage� Detection�

�The� undervoltage� threshold� is� set� at� 50%� of� the� VID� voltage.�

�When� the� output� voltage� at� VSEN� is� below� the� undervoltage�

�threshold,� VR_RDY� gets� pulled� low.� When� the� output�

�voltage� comes� back� to� 60%� of� the� VID� voltage,� VR_RDY� will�

�return� back� to� high.�

�Overvoltage� Protection�

�Regardless� of� the� VR� being� enabled� or� not,� the� ISL6327A�

�t� D2� =� ------------------------� (� μ� s� )�

�1.1xR� SS�

�6.25x25�

�(EQ.� 14)�

�overvoltage� protection� (OVP)� circuit� will� be� active� after� its�

�POR.� The� OVP� thresholds� are� different� under� different�

�operation� conditions.� When� VR� is� not� enabled� and� before�

�For� example,� when� VID� is� set� to� 1.5V� and� the� R� SS� is� set� at�

�100k� Ω� ,� the� soft-start� ramp� time� t� D2� will� be� 704μs.�

�After� the� DAC� voltage� reaches� the� final� VID� setting,�

�VR_RDY� will� be� set� to� high� with� the� fixed� delay� t� D3� .� The�

�typical� value� for� t� D3� is� 85μs.�

�Fault� Monitoring� and� Protection�

�The� ISL6327A� actively� monitors� output� voltage� and� current� to�

�detect� fault� conditions.� Fault� monitors� trigger� protective�

�measures� to� prevent� damage� to� a� microprocessor� load.� One�

�common� power� good� indicator� is� provided� for� linking� to� external�

�system� monitors.� The� schematic� in� Figure� 9� outlines� the�

�interaction� between� the� fault� monitors� and� the� VR_RDY� signal.�

�VR_RDY� Signal�

�The� VR_RDY� pin� is� an� open-drain� logic� output� to� indicate�

�that� the� soft-start� period� is� completed� and� the� output� voltage�

�is� within� the� regulated� range.� VR_RDY� is� pulled� low� during�

�shutdown� and� releases� high� after� a� successful� soft-start� and�

�a� fix� delay� time,� t� D3� .� VR_RDY� will� be� pulled� low� when� an�

�undervoltage,� overvoltage,� or� overcurrent� condition� is�

�19�

�the� 2nd� soft-start,� the� OVP� threshold� is� 1.275V.� Once� the�

�controller� detects� a� valid� VID� input,� the� OVP� trip� point� will� be�

�changed� to� the� VID� voltage� plus� 175mV.�

�Two� actions� are� taken� by� the� ISL6327A� to� protect� the�

�microprocessor� load� when� an� overvoltage� condition� occurs.�

�At� the� inception� of� an� overvoltage� event,� all� PWM� outputs�

�are� commanded� low� instantly� (less� than� 20ns).� This� causes�

�the� Intersil� drivers� to� turn� on� the� lower� MOSFETs� and� pull�

�the� output� voltage� below� a� level� to� avoid� damaging� the� load.�

�When� the� VDIFF� voltage� falls� below� the� DAC� plus� 75mV,�

�PWM� signals� enter� a� high-impedance� state.� The� Intersil�

�drivers� respond� to� the� high-impedance� input� by� turning� off�

�both� upper� and� lower� MOSFETs.� If� the� overvoltage� condition�

�reoccurs,� the� ISL6327A� will� again� command� the� lower�

�MOSFETs� to� turn� on.� The� ISL6327A� will� continue� to� protect�

�the� load� in� this� fashion� as� long� as� the� overvoltage� condition�

�occurs.�

�Once� an� overvoltage� condition� is� detected,� normal� PWM�

�operation� ceases� until� the� ISL6327A� is� reset.� Cycling� the�

�voltage� on� EN_PWR,� EN_VTT� or� VCC� below� the� POR�

�FN6833.0�

�February� 17,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6327IRZ | IC REG CTRLR BUCK PWM 48-QFN |

| ISL6328AIRZ | IC VOLTAGE REGULATOR |

| ISL6328IRZ | IC CTRLR PWM SYNC BUCK DL 48QFN |

| ISL6329IRZ-T | IC CTRLR PWM SYNC BUCK DL 60QFN |

| ISL6333IRZ | IC CTRLR PWM 3PHASE BUCK 48-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6327AIRZ-T | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6327CRZ | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6327CRZ-T | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6327IRZ | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6327IRZ-T | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。