参数资料

| 型号: | ISL6564AIRZ |

| 厂商: | Intersil |

| 文件页数: | 14/28页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 40-QFN |

| 标准包装: | 500 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 1.5MHz |

| 占空比: | 66.7% |

| 电源电压: | 4.75 V ~ 5.25 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

�

�ISL6564A�

�L�

�L�

�I�

�R� SENSE� V� OUT�

�Channel-Current� Balance�

�The� sampled� currents� I� n� ,� from� each� active� channel� are�

�ISL6564A� INTERNAL� CIRCUIT�

�C� OUT�

�summed� together� and� divided� by� the� number� of� active�

�channels.� The� resulting� cycle� average� current� I� AVG� ,� provides�

�a� measure� of� the� total� load� current� demand� on� the� converter�

�during� each� switching� cycle.� Channel� current� balance� is�

�I� n�

�SAMPLE�

�&�

�HOLD�

�+�

�ISEN-(n)�

�R� ISEN(n)�

�achieved� by� comparing� the� sampled� current� of� each� channel�

�to� the� cycle� average� current,� and� making� an� appropriate�

�adjustment� to� each� channel� pulse� width� based� on� the� error.�

�Intersil’s� patented� current-balance� method� is� illustrated� in�

�Figure� 7,� with� error� correction� for� channel� 1� represented.� In�

�-�

�ISEN+(n)�

�the� figure,� the� cycle� average� current� combines� with� the�

�channel� 1� sample,� I� 1� ,� to� create� an� error� signal� I� ER� .� The�

�I�

�R�

�R� SENSE�

�SEN� =� I� L� --------------------------�

�ISEN�

�filtered� error� signal� modifies� the� pulse� width� commanded� by�

�V� COMP� to� correct� any� unbalance� and� force� I� ER� toward� zero.�

�FIGURE� 5.� SENSE� RESISTOR� IN� SERIES� WITH� INDUCTORS�

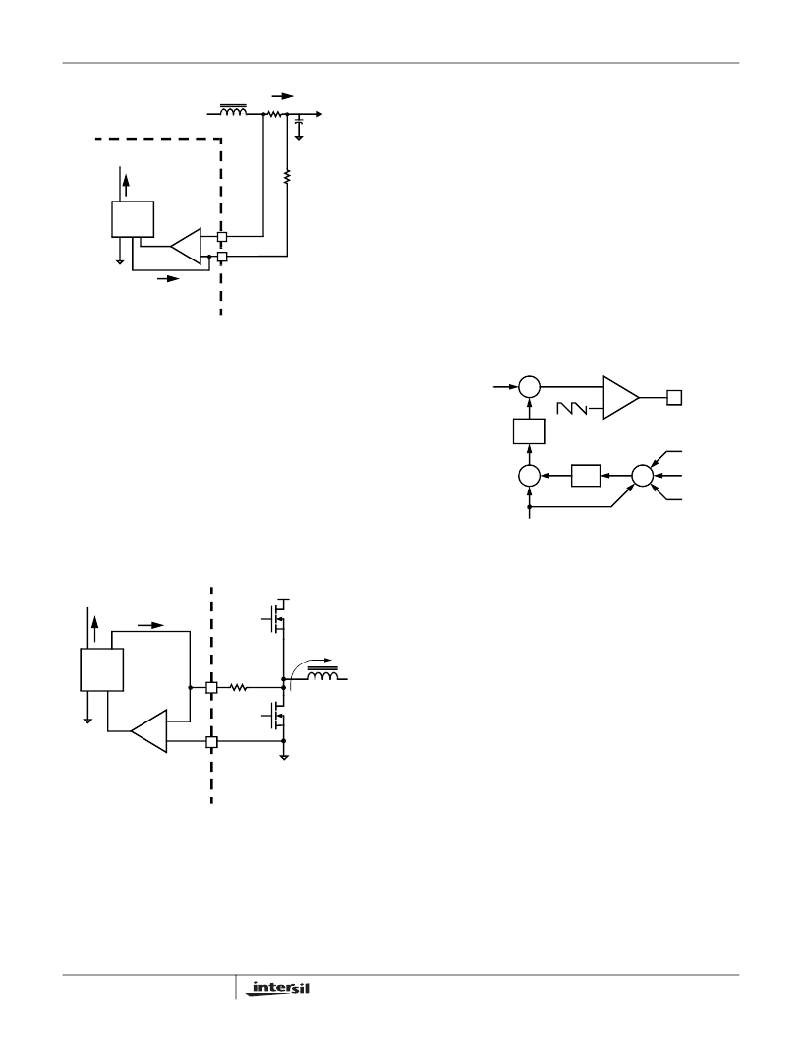

�MOSFET� r� DS(ON)� SENSING�

�The� same� method� for� error� signal� correction� is� applied� to�

�each� active� channel.�

�The� controller� can� also� sense� the� channel� load� current� by�

�sampling� the� voltage� across� the� lower� MOSFET� r� DS(ON)�

�(see� Figure� 6).� The� amplifier� is� ground-reference� by�

�connecting� the� ISEN-� input� to� the� source� of� the� lower�

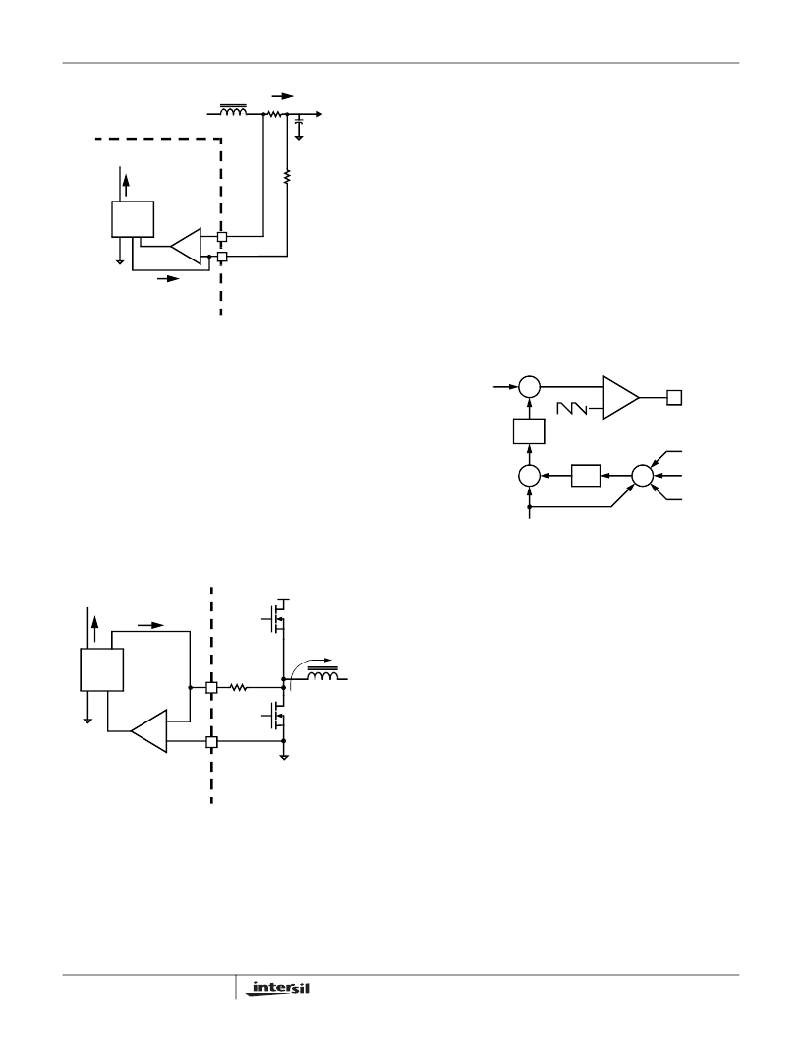

�V� COMP�

�FILTER�

�+�

�-�

�f(j� ω� )�

�+�

�-�

�SAWTOOTH� SIGNAL�

�PWM1�

�MOSFET.� ISEN+� connects� to� the� PHASE� node� through� a�

�resistor� R� ISEN� .� The� voltage� across� R� ISEN� is� equivalent� to�

�the� voltage� drop� across� the� r� DS(ON)� of� the� lower� MOSFET�

�while� it� is� conducting.� The� resulting� current� into� the� ISEN+�

�pin� is� proportional� to� the� channel� current� I� L� .� The� ISEN�

�I� ER�

�+�

�-�

�I� AVG�

�÷� N�

�Σ�

�I� 4� *�

�I� 3� *�

�I� 2�

�current� is� then� sampled� and� held� after� sufficient� settling� time.�

�The� sampled� current� I� n� ,� is� used� for� channel-current� balance,�

�load-line� regulation,� and� overcurrent� protection.� From�

�Figure� 6,� Equation� 7� for� I� SEN� is� derived.�

�I� 1�

�NOTE:� *Channels� 3� and� 4� are� optional.�

�FIGURE� 7.� CHANNEL� 1� PWM� FUNCTION� AND� CURRENT-�

�I� SEN� =� I� -------------------------� )� -�

�DS� (� ON�

�L� R�

�I� n�

�r�

�ISEN�

�V� IN�

�BALANCE� ADJUSTMENT�

�Channel� current� balance� is� essential� in� realizing� the� thermal�

�advantage� of� multiphase� operation.� The� heat� generated� in�

�SAMPLE�

�&�

�HOLD�

�ISEN+(n)�

�I� L�

�down� converting� is� dissipated� over� multiple� devices� and� a�

�greater� area.� The� designer� avoids� the� complexity� of� driving�

�multiple� parallel� MOSFETs,� and� the� expense� of� using� heat�

�L� DS� (� ON� )�

�-�

�R� ISEN�

�(PTC)�

�ISEN-(n)�

�-�

�I�

�+�

�r�

�sinks� and� nonstandard� magnetic� materials.�

�Voltage� Regulation�

�+�

�N-CHANNEL�

�MOSFETs�

�The� integrating� compensation� network� shown� in� Figure� 8�

�assures� that� the� steady-state� error� in� the� output� voltage� is�

�limited� only� to� the� error� in� the� reference� voltage� (output� of�

�ISL6564A� INTERNAL� CIRCUIT�

�EXTERNAL� CIRCUIT�

�the� DAC)� and� offset� errors� in� the� OFS� current� source,�

�remote-sense� and� error� amplifiers.� Intersil� specifies� the�

�FIGURE� 6.� MOSFET� r� DS(ON)� CURRENT-SENSING� CIRCUIT�

�guaranteed� tolerance� of� the� ISL6564A� to� include� the�

�combined� tolerances� of� each� of� these� elements.�

�I� SEN� =� I� L� ----------------------� )�

�r� DS� (� ON�

�R� ISEN�

�(EQ.� 7)�

�The� output� of� the� error� amplifier,� V� COMP� ,� is� compared� to� the�

�sawtooth� waveform� to� generate� the� PWM� signals.� The� PWM�

�where� I� L� is� the� channel� current.� Since� MOSFET� r� DS(ON)�

�increases� with� temperature,� a� PTC� resistor� should� be�

�chosen� for� R� ISEN� to� compensate� for� this� change.�

�14�

�signals� control� the� timing� of� the� Intersil� MOSFET� drivers� and�

�regulate� the� converter� output� to� the� specified� reference�

�voltage.� The� internal� and� external� circuitry� which� control�

�voltage� regulation� is� illustrated� in� Figure� 8.�

�FN6285.1�

�March� 20,� 2007�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6564IR-T | IC REG CTRLR BUCK PWM VM 40-QFN |

| ISL6565BCV-T | IC REG CTRLR BUCK PWM VM 28TSSOP |

| ISL6566AIRZ | IC CTRLR PWM 3PHASE BUCK 40-QFN |

| ISL6566CRZ-T | IC CTLR PWM BUCK 3PHASE 40-QFN |

| ISL6567CRZ | IC REG CTRLR BUCK PWM VM 24-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6564AIRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6564CR | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:4,000 系列:- PWM 型:电压模式 输出数:1 频率 - 最大:1.5MHz 占空比:66.7% 电源电压:4.75 V ~ 5.25 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-40°C ~ 85°C 封装/外壳:40-VFQFN 裸露焊盘 包装:带卷 (TR) |

| ISL6564CR-T | 功能描述:IC REG CTRLR BUCK PWM VM 40-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:4,000 系列:- PWM 型:电压模式 输出数:1 频率 - 最大:1.5MHz 占空比:66.7% 电源电压:4.75 V ~ 5.25 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-40°C ~ 85°C 封装/外壳:40-VFQFN 裸露焊盘 包装:带卷 (TR) |

| ISL6564CRZ | 功能描述:电流型 PWM 控制器 LEAD-FREE MULTI-PHASE PWM CONTROLLER W/ 0.525-1.3 VID RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6564CRZ-T | 功能描述:电流型 PWM 控制器 LEAD-FREE MULTI-PHASE PWM CONTROLLER W/ 0.525-1.3 VID, T&R RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

发布紧急采购,3分钟左右您将得到回复。