参数资料

| 型号: | ISL6568IRZ-TR5184 |

| 厂商: | Intersil |

| 文件页数: | 18/30页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM 2PHASE BUCK 32-QFN |

| 标准包装: | 6,000 |

| 应用: | 控制器,Intel VRM9,VRM10,AMD Hammer 应用 |

| 输入电压: | 3 V ~ 12 V |

| 输出数: | 1 |

| 输出电压: | 0.84 V ~ 1.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�ISL6568�

�Thus,� the� soft-start� period� (not� including� the� 16� PHASE� clock�

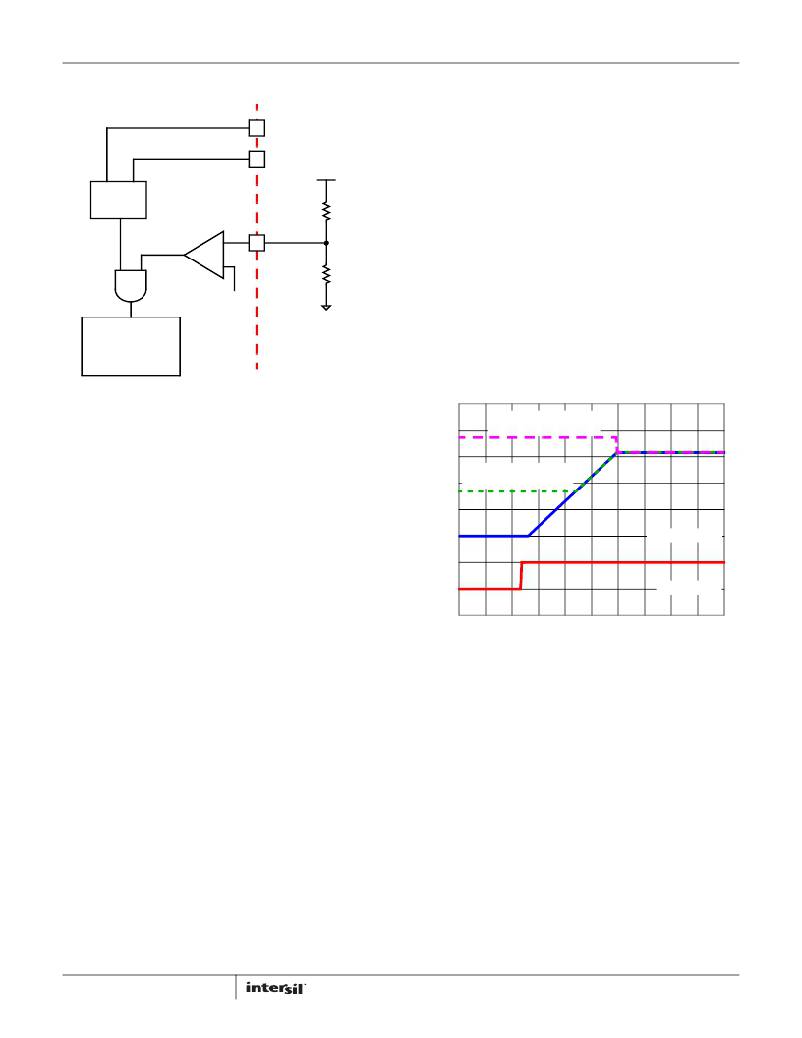

�ISL6568� INTERNAL� CIRCUIT�

�EXTERNAL� CIRCUIT�

�cycle� delay)� up� to� a� given� voltage,� V� DAC� ,� can� be� approximated�

�by� Equation� 13.�

�T� SS� =� ---------------------------------�

�VCC�

�PVCC1�

�V� DAC� ?� 1280�

�f� S�

�(EQ.� 13)�

�POR�

�+� 12� V�

�where� V� DAC� is� the� DAC-set� VID� voltage,� and� f� S� is� the� switching�

�frequency.�

�CIRCUIT�

�ENABLE�

�COMPARATOR�

�+�

�-�

�10.7k� Ω�

�ENLL�

�1.40k� Ω�

�The� ISL6568� also� has� the� ability� to� start� up� into� a� pre-charged�

�output,� without� causing� any� unnecessary� disturbance.� The� FB�

�pin� is� monitored� during� soft-start,� and� should� it� be� higher� than�

�the� equivalent� internal� ramping� reference� voltage,� the� output�

�drives� hold� both� MOSFETs� off.� Once� the� internal� ramping�

�reference� exceeds� the� FB� pin� potential,� the� output� drives� are�

�SOFT-START�

�AND�

�FAULT� LOGIC�

�0.66V�

�enabled,� allowing� the� output� to� ramp� from� the� pre-charged�

�level� to� the� final� level� dictated� by� the� DAC� setting.� Should� the�

�output� be� pre-charged� to� a� level� exceeding� the� DAC� setting,� the�

�output� drives� are� enabled� at� the� end� of� the� soft-start� period,�

�leading� to� an� abrupt� correction� in� the� output� voltage� down� to�

�the� DAC-set� level.�

�FIGURE� 11.� POWER� SEQUENCING� USING� THRESHOLD-SENSITIVE�

�ENABLE� (ENLL)� FUNCTION�

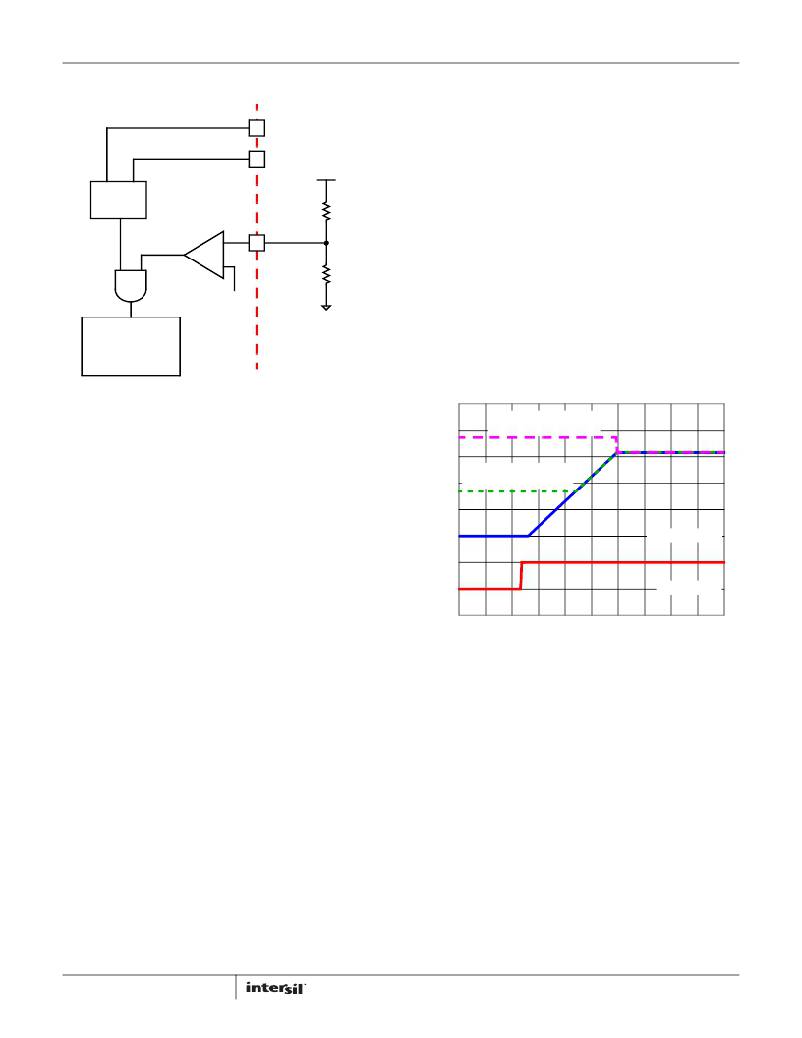

�OUTPUT� PRECHARGED�

�ABOVE� DAC� LEVEL�

�2.� The� voltage� on� ENLL� must� be� above� 0.66V.� The� EN� input�

�allows� for� power� sequencing� between� the� controller� bias�

�voltage� and� another� voltage� rail.� The� enable� comparator�

�holds� the� ISL6568� in� shutdown� until� the� voltage� at� ENLL�

�rises� above� 0.66V.� The� enable� comparator� has� 60mV� of�

�hysteresis� to� prevent� bounce.�

�OUTPUT� PRECHARGED�

�BELOW� DAC� LEVEL�

�3.� The� driver� bias� voltage� applied� at� the� PVCC� pin� must� reach�

�the� internal� power-on� reset� (POR)� rising� threshold.�

�Hysteresis� between� the� rising� and� falling� thresholds� assure�

�that� once� enabled,� the� ISL6568� will� not� inadvertently� turn�

�off� unless� the� PVCC� bias� voltage� drops� substantially� (see�

�“Electrical� Specifications”� on� page� 6).�

�4.� The� VID� code� must� not� be� 111111� or� 111110� in� VRM10�

�GND>�

�GND>�

�T1� T2�

�T3�

�V� OUT� (0.5V/DIV)�

�ENLL� (5V/DIV)�

�mode� or� 11111� in� AMD� Hammer� or� VRM9� modes.� These�

�codes� signal� the� controller� that� no� load� is� present.� The�

�controller� will� enter� shut-down� mode� after� receiving� either�

�of� these� codes� and� will� execute� soft-start� upon� receiving�

�any� other� code.� These� codes� can� be� used� to� enable� or�

�disable� the� controller� but� it� is� not� recommended.� After�

�receiving� one� of� these� codes,� the� controller� executes� a�

�2-cycle� delay� before� changing� the� overvoltage� trip� level� to�

�the� shut-down� level� and� disabling� PWM.� Overvoltage�

�shutdown� cannot� be� reset� using� one� of� these� codes.�

�When� each� of� these� conditions� is� true,� the� controller�

�immediately� begins� the� soft-start� sequence.�

�SOFT-START�

�The� soft-start� function� allows� the� converter� to� bring� up� the�

�output� voltage� in� a� controlled� fashion,� resulting� in� a� linear�

�ramp-up.� Following� a� delay� of� 16� PHASE� clock� cycles� between�

�enabling� the� chip� and� the� start� of� the� ramp,� the� output� voltage�

�progresses� at� a� fixed� rate� of� 12.5mV� per� each� 16� PHASE� clock�

�cycles.�

�18�

�FIGURE� 12.� SOFT-START� WAVEFORMS� FOR� ISL6568-BASED�

�MULTI-PHASE� CONVERTER�

�Fault� Monitoring� and� Protection�

�The� ISL6568� actively� monitors� output� voltage� and� current� to�

�detect� fault� conditions.� Fault� monitors� trigger� protective�

�measures� to� prevent� damage� to� a� microprocessor� load.� One�

�common� power� good� indicator� is� provided� for� linking� to�

�external� system� monitors.� The� schematic� in� Figure� 13� outlines�

�the� interaction� between� the� fault� monitors� and� the� power� good�

�signal.�

�FN9187.5�

�January� 12,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6568IRZA-T | IC CTRLR PWM BUCK 2PHASE 32-QFN |

| MIC5320-MFYML TR | IC REG LDO 2.8V/1.5V .15A 6-MLF |

| ISL6568IRZ-T | IC CTRLR PWM BUCK 2PHASE 32-QFN |

| LT1175CS8#PBF | IC REG LDO NEG ADJ .5A 8SOIC |

| ABC17DRES | CONN EDGECARD 34POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6569ACB | 功能描述:IC REG CTRLR BUCK PWM 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6569ACB-T | 功能描述:IC REG CTRLR BUCK PWM 24-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6569ACBZ | 功能描述:IC REG CTRLR BUCK PWM 24-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6569ACBZ-T | 功能描述:IC REG CTRLR BUCK PWM 24-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6569ACR | 功能描述:IC REG CTRLR BUCK PWM 32-QFN RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。