- 您现在的位置:买卖IC网 > PDF目录15524 > ISL6726AAZ (Intersil)IC REG CTRLR ISO PWM CM 20-QSOP PDF资料下载

参数资料

| 型号: | ISL6726AAZ |

| 厂商: | Intersil |

| 文件页数: | 13/20页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR ISO PWM CM 20-QSOP |

| 标准包装: | 58 |

| PWM 型: | 电流模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 100% |

| 电源电压: | 9 V ~ 16 V |

| 降压: | 无 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 是 |

| 工作温度: | -40°C ~ 105°C |

| 封装/外壳: | 20-SSOP(0.154",3.90mm 宽) |

| 包装: | 管件 |

�� �

�

�

�ISL6726�

�avalanche� when� the� duty� cycle� becomes� non-zero.� When� the�

�forward� SR� turns� on,� the� inductor� current� will� reflect� to� the�

�1.2(V� ERR� -V� OFFSET� )�

�V� SS� =5V-I� SS� *t/C� SS�

�Soft-stop� ends�

�primary� and� stress� the� components� there� as� well.� With� the�

�minimum� duty� cycle� clamp� feature,� the� forward� rectifier� turns� on�

�Soft-stop� begins�

�for� ~300ns� each� cycle� and� prevents� the� large� negative� current� in�

�OUTM�

�OUTAC�

�0.27V�

�0.0V�

�the� output� inductor.�

�Gate� Drive�

�The� ISL6726� has� two� outputs,� OUTM� and� OUTAC.� OUTM� is�

�capable� of� sourcing� 1A� and� sinking� 1.5A� peak� current,� and�

�OUTAC� is� capable� of� sourcing� 0.5A� and� sinking� 0.75A� peak�

�CS�

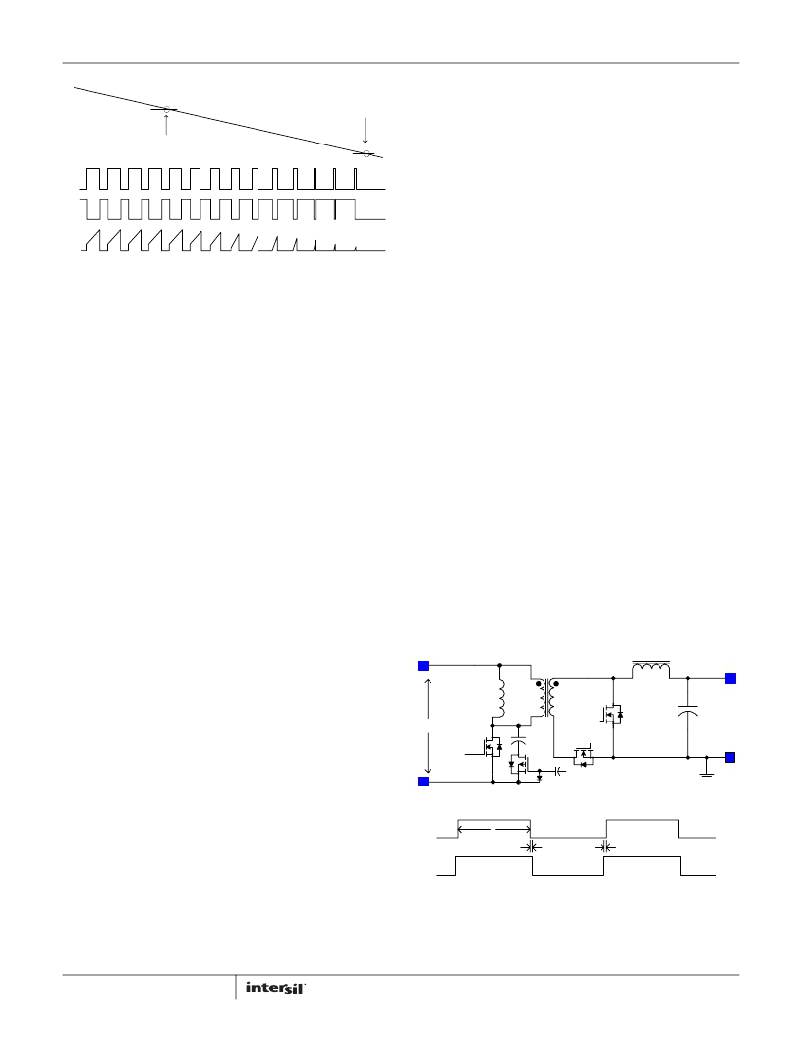

�FIGURE� 8.� SOFT-STOP� FUNCTION� (I� DELAY� POSITIVE)�

�The� soft-stop� function� is� enabled� when� MODE=0.� The� ISL6726�

�enables� a� soft-stop� when� UV� falls� below� 1V� or� when� ENABLE� is�

�pulled� low� (disable),� causing� a� controlled� discharge� of� the� SS�

�capacitor� at� the� rate� equal� to� and� opposite� of� soft-start.� Soft-stop�

�will� not� occur� for� a� UVLO� fault� on� VDD� regardless� of� the� MODE�

�setting.� Soft-stop� continues� until� the� SS� pin� voltage� drops� below�

�~0.25V,� even� if� the� fault� condition� is� removed� before� the�

�threshold� is� reached.�

�Using� soft-stop� forces� an� orderly� shutdown� of� a� converter� that�

�uses� synchronous� rectification� (SR).� It� prevents� the� output�

�voltage� from� going� negative� by� controlling� the� rate� at� which� the�

�output� voltage� is� discharged� through� the� output� inductor.� It� also�

�prevents� the� SRs� from� being� avalanched� if� SR� operation� is�

�stopped� when� the� inductor� current� is� negative.�

�If� a� self-driven� SR� method� is� used,� the� behavior� during� turn-off� is�

�improved� as� well.� During� soft-stop,� the� forward� rectifier� pulse�

�width� is� slowly� decreased� to� its� minimum� while� the�

�free-wheeling� rectifier� pulse� width� is� slowly� increased� to� its�

�maximum.� The� active� clamp� capacitor� voltage,� V� IN� /(1-D),�

�approaches� V� IN� as� the� duty� cycle� approaches� zero.� The�

�freewheeling� rectifier� gate� voltage� is� V� IN� D/n(1-D),� where� n� is� the�

�transformer� turns� ratio� Np/Ns,� and� decreases� with� decreasing�

�duty� cycle.� At� some� point� the� voltage� applied� to� the� gate� is�

�insufficient� to� turn� on� the� SR� FET� and� negative� inductor� current�

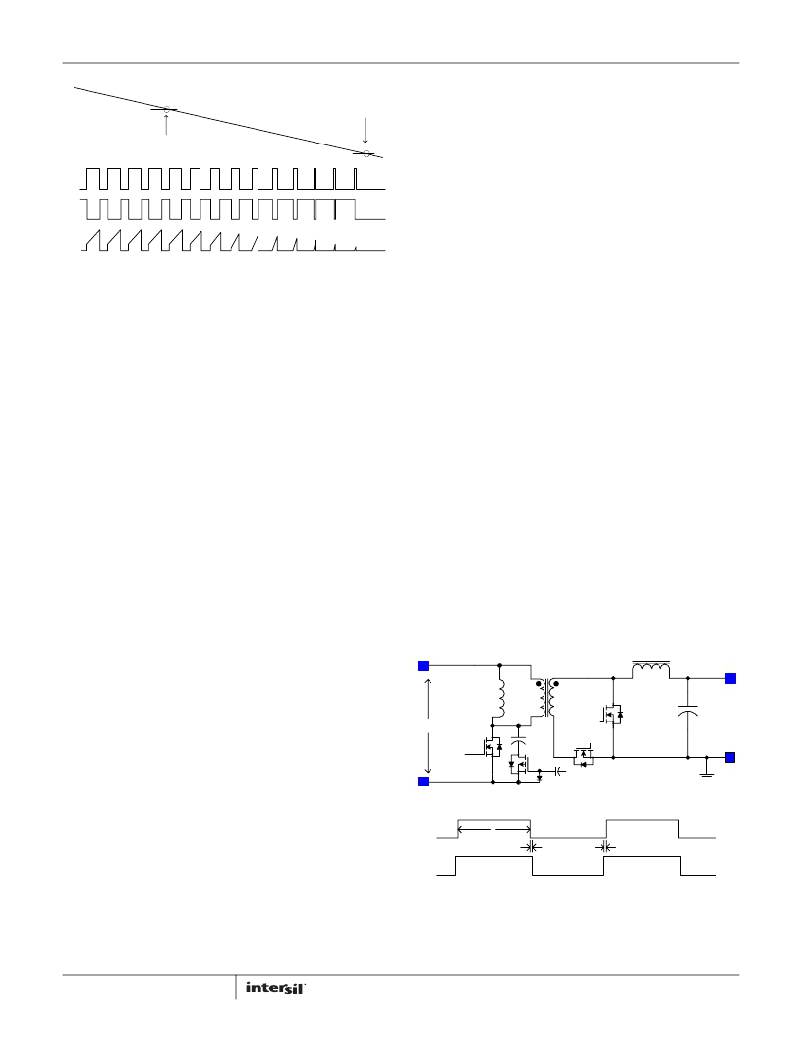

�current.� OUTAC� is� configured� using� the� DELAY� input� for� either�

�overlap� or� non-overlap� phasing� relative� to� OUTM.� When�

�configured� for� non-overlap� phasing,� OUTAC� operates� at� 1-D� with�

�deadtime,� where� D� is� the� duty� cycle� of� OUTM.� This� configuration�

�is� useful� for� the� n-channel� active� clamp� and� asymmetric� half-�

�bridge� topologies.� When� configured� for� overlap� phasing,� OUTAC�

�has� symmetric� rising� edge� advance� and� falling� edge� delays�

�relative� to� OUTM.� This� configuration� is� useful� for� the� p-channel�

�active� clamp� topology.�

�Two� typical� active� clamp� converter� configurations� are� shown� in�

�Figures� 9� and� 10,� with� overlap� or� non-overlap� delay� time�

�accurately� set� by� a� programming� resistor.� The� rising� edge�

�overlap� and� the� falling� edge� overlap� time� (or� rising� edge�

�deadtime,� and� falling� edge� deadtime)� are� equal� and�

�independent� of� the� operating� frequency� or� duty� cycle.�

�To� limit� the� peak� current� through� the� IC,� an� external� resistor� may�

�be� placed� in� series� between� an� output� and� the� gate� of� the�

�MOSFET.� The� resistor� also� dampens� any� oscillation� caused� by�

�the� resonant� tank� of� the� parasitic� inductance� of� the� PWB� traces�

�and� the� FET� gate� input� capacitance.� The� overlap/non-overlap�

�delay� between� OUTAC� and� OUTM� prevents� simultaneous�

�conduction� of� the� main� and� clamp� switches� in� an� active� clamp�

�converter,� or� the� upper� and� lower� switches� in� an� asymmetric�

�half-� bridge� converter.�

�Table� 1� shows� the� combinations� of� the� settings� with� the�

�corresponding� features� for� different� topologies.�

�is� prevented.�

�A� hard-stop� with� self-driven� SRs� results� in� oscillation� of� the� SRs�

�because� the� output� voltage� can� provide� gate� voltage� through� the�

�output� inductor� and� secondary� winding.�

�Lm�

�Tx�

�VX�

�+�

�+VOUT�

�Minimum� Duty� Cycle� Clamp�

�In� addition� to� soft-stop� when� MODE=0,� the� minimum� pulse� width�

�OUTM�

�VY�

�of� OUTM� is� clamped� to� ~300ns� independent� of� the� PWM�

�modulator.� Higher� duty� cycles� are� obviously� allowed� depending� on�

�the� operating� conditions,� but� shorter� duty� cycles� are� not.� In� SR�

�applications,� this� feature� prevents� excessive� negative� output�

�OUTAC�

�Vout� =� Vin*D*Ns/Np�

�inductor� current� if� the� output� should� experience� a� large� and�

�OUTM�

�D�

�sudden� reduction� in� load,� such� as� occurs� during� a� 100%� to� 0%�

�load� transient.� A� sudden� load� dump� can� cause� the� control� loop�

�error� voltage� to� drop� sufficiently� to� command� 0%� duty� cycle.� This�

�sets� the� forward� rectifier� to� 0%� duty� cycle� and� the� free-wheeling�

�OUTAC�

�Td� =� K1*Rdelay�

�Td� =� K1*Rdelay�

�rectifier� to� 100%� duty� cycle.� This� condition� allows� the� inductor�

�current� to� ramp� to� a� large� negative� amplitude� until� the� duty� cycle�

�again� becomes� non-zero.� Due� to� the� normal� deadtime� allowed�

�for� proper� switching� of� the� SRs,� the� forward� rectifier� will�

�13�

�FIGURE� 9.� OUTPUT� TIMING� DIAGRAM� FOR� P-CHANNEL� ACTIVE�

�CLAMP�

�FN7654.0�

�January� 31,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| RGM08DTAT | CONN EDGECARD 16POS R/A .156 SLD |

| 0819-94K | COIL RF 820UH MOLDED UNSHIELDED |

| ISL6742AAZA | IC REG CTRLR PWM CM/VM 16-QSOP |

| VI-J5D-EY | CONVERTER MOD DC/DC 85V 50W |

| RCM18DTAT | CONN EDGECARD 36POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6726AAZ-T | 功能描述:IC REG CTRLR ISO PWM CM 20-QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6726AAZ-T7A | 功能描述:IC REG CTRLR ISO PWM CM 20-QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6726EVAL1Z | 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 LD QSOP - ROHS COMPLIAN - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ISL6726 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 Ld QSOP - ROHS COMPLIAN |

| ISL6729IB | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6729IB-T | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。