- 您现在的位置:买卖IC网 > PDF目录15524 > ISL6726AAZ (Intersil)IC REG CTRLR ISO PWM CM 20-QSOP PDF资料下载

参数资料

| 型号: | ISL6726AAZ |

| 厂商: | Intersil |

| 文件页数: | 15/20页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR ISO PWM CM 20-QSOP |

| 标准包装: | 58 |

| PWM 型: | 电流模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 100% |

| 电源电压: | 9 V ~ 16 V |

| 降压: | 无 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 是 |

| 工作温度: | -40°C ~ 105°C |

| 封装/外壳: | 20-SSOP(0.154",3.90mm 宽) |

| 包装: | 管件 |

�� �

�

�

�ISL6726�

�(VERR)� used� by� the� pulse� width� modulator.� Whichever� error�

�signal,� voltage� or� current,� that� commands� the� lower� duty� cycle� is�

�in� control.� If� the� average� current� is� lower� than� the� average�

�current� limit� threshold,� the� current� error� amplifier� has� no� impact�

�on� VERR� and� the� voltage� loop� is� in� control.� If� the� average� current�

�limit� threshold� is� exceeded,� however,� the� current� error� amplifier�

�will� lower� VERR� to� regulate� the� output� current.� The� voltage� loop�

�loses� control� as� it� must� increase� the� duty� cycle� to� maintain� the�

�output� voltage� in� regulation.�

�After� a� 100ns� leading� edge� blanking� (LEB)� delay,� the� current�

�sense� signal� is� sampled� for� the� duration� of� the� on� time,� the�

�average� current� is� determined,� and� the� result� is� amplified� by� 4x�

�and� output� to� the� IOUT� pin� at� the� termination� of� the� OUTM� pulse.�

�Due� to� the� sampling� algorithm� used,� if� an� RC� filter� is� placed� on�

�the� CS� input,� its� time� constant� should� not� exceed� ~30ns� or� error�

�may� be� introduced� on� IOUT.�

�inductor� current� becomes� discontinuous� (DCM� operation),� IOUT�

�represents� one� half� of� the� peak� inductor� current� rather� than� the�

�average� current.� This� occurs� because� the� sample� and� hold�

�circuitry� is� active� only� during� the� on� time� of� the� switching� cycle�

�and� cannot� determine� when� the� inductor� current� becomes�

�discontinuous.� It� is� unable� to� detect� when� the� inductor� current�

�reaches� zero� during� the� off� time.� This� behavior� does� not� affect�

�the� average� current� limit� function,� but� does� have� an� impact� if�

�IOUT� is� used� for� current� monitoring� functions.�

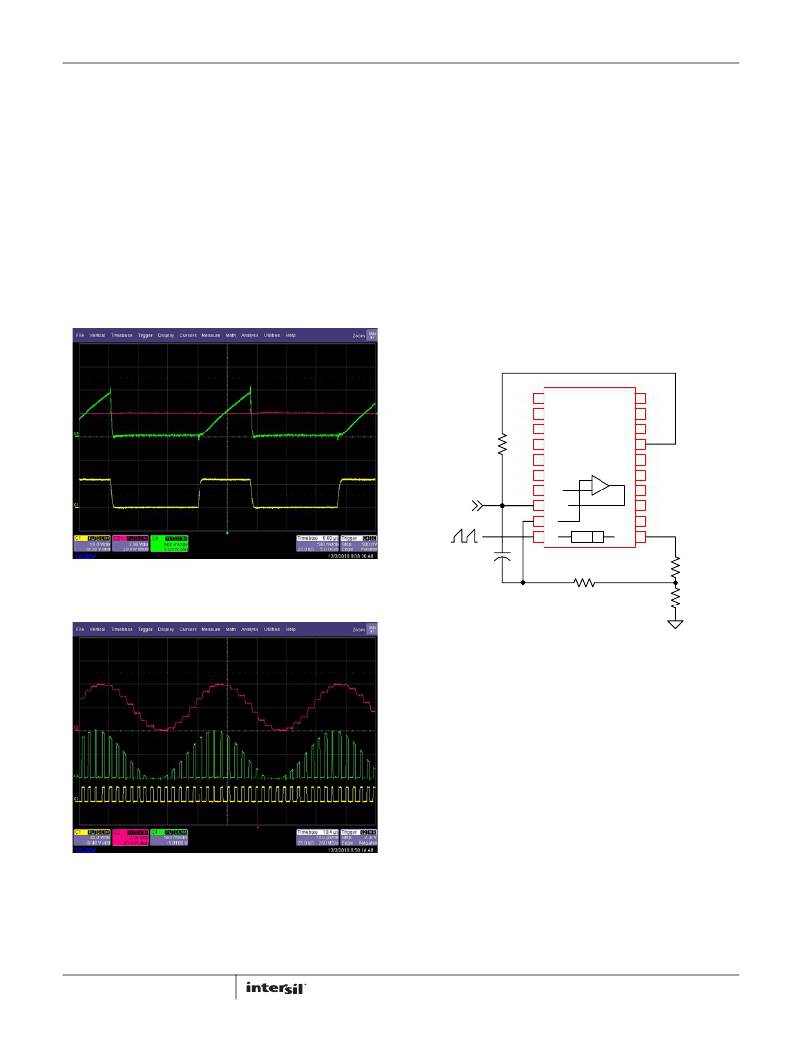

�IOUT� may� be� used� with� the� available� error� amplifier� (EA)� of� the�

�ISL6726� as� shown� in� Figure� 13.� The� error� amplifier� is� typically�

�configured� as� an� integrator.� As� shown� in� Figure� 13,� IOUT� is�

�attenuated� by� resistors� R� 1� and� R� 2� so� that� the� average� current�

�limit� threshold� can� be� set� independently� of� the� peak� current�

�limit� threshold.� The� integrator� bandwidth� is� determined� by� R� and�

�C.� The� current� error� amplifier� is� similar� to� the� voltage� EA� found� in�

�most� PWM� controllers,� except� it� cannot� source� current.� VERR�

�requires� an� external� pull-up� resistor.�

�1�

�20�

�2�

�3�

�ISL6726�

�19�

�18�

�R� PULL-UP�

�4�

�5�

�VREF� 17�

�16�

�C�

�6�

�7� ISET�

�8� VERR�

�9� FB�

�10� CS�

�-�

�+�

�S&H 4x�

�15�

�14�

�13�

�12�

�IOUT� 11�

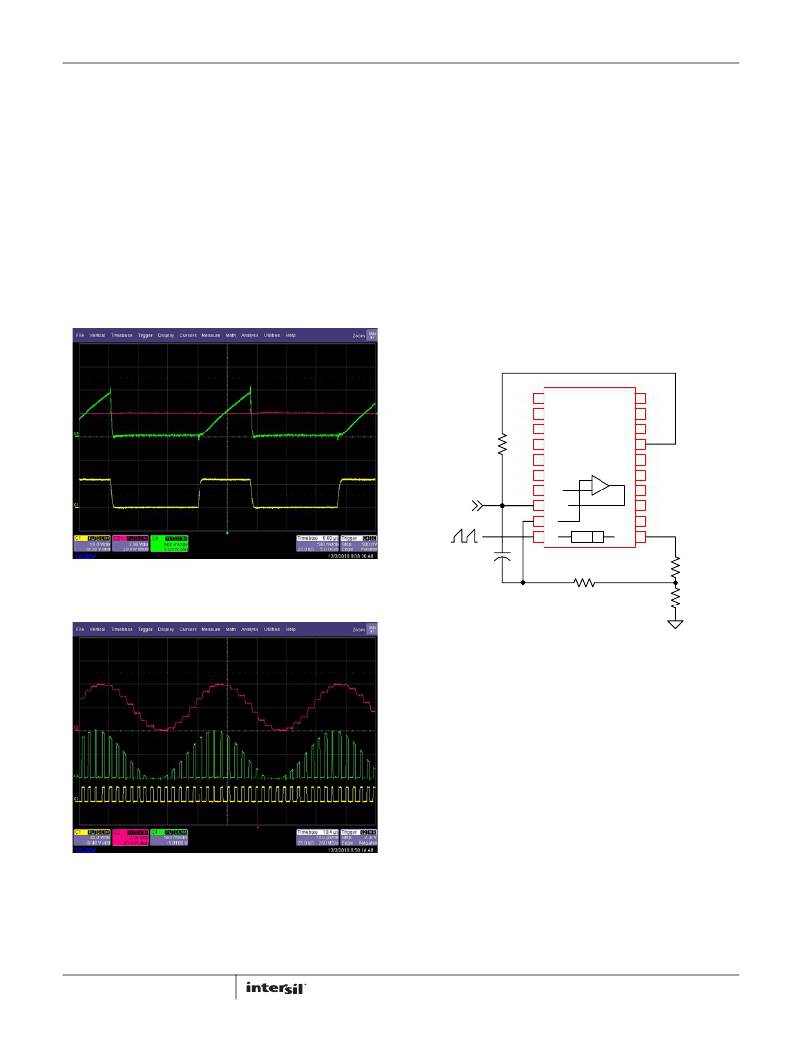

�Channel� ?� 1:� ?� OUTM� ?�

�?????????????� Channel� ?� 2:� ?� IOUT� ?�

�??????????????� Channel� ?� 4:� ?� CS�

�R�

�R1�

�FIGURE� 11.� CS� INPUT� vs� IOUT�

�R2�

�FIGURE� 13.� AVERAGE� CURRENT� CONFIGURATION�

�The� IEA� is� configured� as� an� integrating� (Type� I)� amplifier� using�

�ISET� as� the� reference.� The� voltage� applied� at� FB� is� integrated�

�against� the� ISET� reference.� The� resulting� signal,� VERR,� is� applied�

�to� the� PWM� comparator� where� it� is� compared� to� the� current�

�signal� CS.� If� FB� is� less� than� ISET,� the� IEA� will� be� open� loop� (can’t�

�source� current),� VERR� will� be� at� a� level� determined� by� the�

�voltage� loop,� and� the� duty� cycle� is� unaffected.� As� the� output� load�

�increases,� IOUT� will� increase,� and� the� voltage� applied� to� FB� will�

�increase� until� it� reaches� ISET.� At� this� point� the� IEA� will� control�

�VERR� as� required� to� maintain� the� output� current� at� the� level� that�

�corresponds� to� the� ISET� reference.� When� the� output� current�

�again� drops� below� the� average� current� limit� threshold,� the� IEA�

�Channel� ?� 1:� ?� OUTM� ?�

�?????????????� Channel� ?� 2:� ?� IOUT� ?�

�??????????????� Channel� ?� 4:� ?� CS�

�returns� to� an� open� loop� condition,� and� the� duty� cycle� is� again�

�controlled� by� the� voltage� loop.� The� average� current� control� loop�

�FIGURE� 12.� DYNAMIC� BEHAVIOR� OF� CS� AND� IOUT�

�The� average� current� signal� on� IOUT� produces� an� accurate�

�representation� of� the� output� current� provided� the� converter�

�operates� in� continuous� conduction� mode� (CCM).� Once� the�

�15�

�behaves� much� the� same� as� the� voltage� control� loop� found� in�

�typical� power� supplies� except� it� regulates� current� rather� than�

�voltage.�

�FN7654.0�

�January� 31,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| RGM08DTAT | CONN EDGECARD 16POS R/A .156 SLD |

| 0819-94K | COIL RF 820UH MOLDED UNSHIELDED |

| ISL6742AAZA | IC REG CTRLR PWM CM/VM 16-QSOP |

| VI-J5D-EY | CONVERTER MOD DC/DC 85V 50W |

| RCM18DTAT | CONN EDGECARD 36POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6726AAZ-T | 功能描述:IC REG CTRLR ISO PWM CM 20-QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6726AAZ-T7A | 功能描述:IC REG CTRLR ISO PWM CM 20-QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6726EVAL1Z | 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 LD QSOP - ROHS COMPLIAN - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ISL6726 制造商:Intersil Corporation 功能描述:ISL6726 EVALUATION BOARD 1 - 20 Ld QSOP - ROHS COMPLIAN |

| ISL6729IB | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

| ISL6729IB-T | 功能描述:IC REG CTRLR BST FLYBK ISO 8SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:500kHz 占空比:100% 电源电压:8.2 V ~ 30 V 降压:无 升压:无 回扫:是 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:0°C ~ 70°C 封装/外壳:8-DIP(0.300",7.62mm) 包装:管件 产品目录页面:1316 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。