- 您现在的位置:买卖IC网 > PDF目录15216 > ISL8105AIRZ-T (Intersil)IC REG CTRLR BUCK PWM VM 10-DFN PDF资料下载

参数资料

| 型号: | ISL8105AIRZ-T |

| 厂商: | Intersil |

| 文件页数: | 12/16页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 10-DFN |

| 标准包装: | 6,000 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 660kHz |

| 占空比: | 100% |

| 电源电压: | 6.5 V ~ 14.4 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 10-VFDFN 裸露焊盘 |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL8105,� ISL8105A�

�frequency� helps� reduce� the� gain� of� the� compensation�

�R� 3� =� --------------------�

�f� SW�

�network� at� high� frequency,� in� turn� reducing� the� HF� ripple�

�component� at� the� COMP� pin� and� minimizing� resultant�

�duty� cycle� jitter.�

�R� 1�

�-----------� –� 1�

�(EQ.� 8)�

�F� LC�

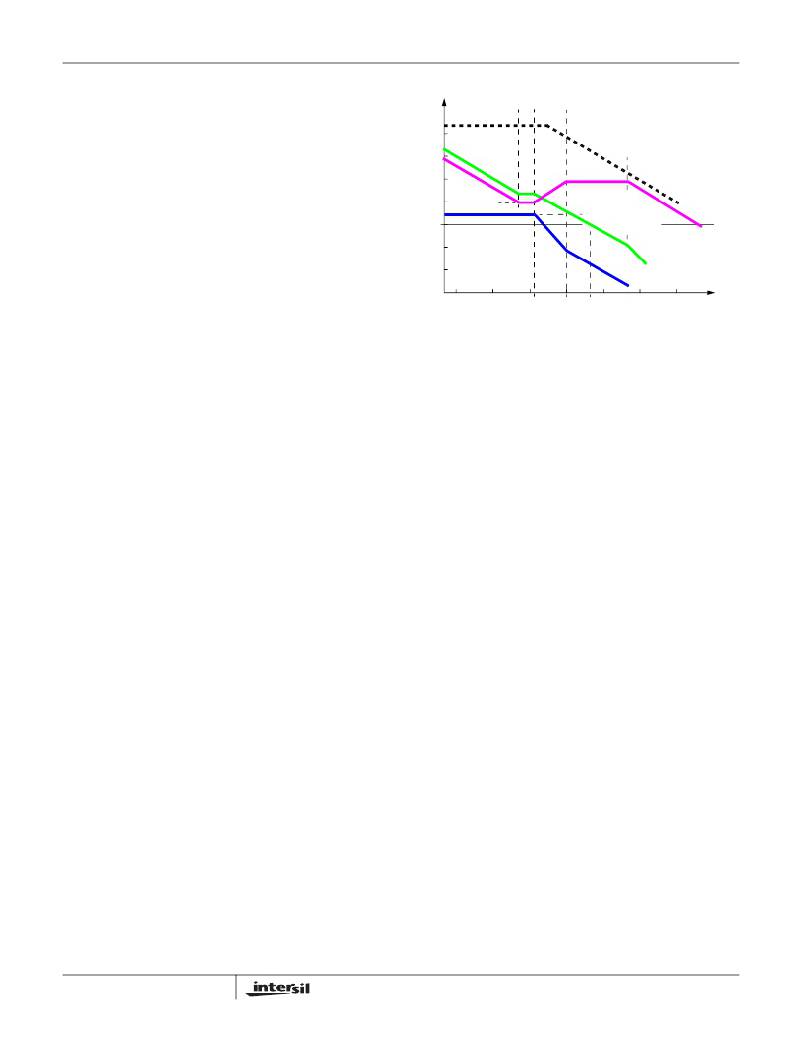

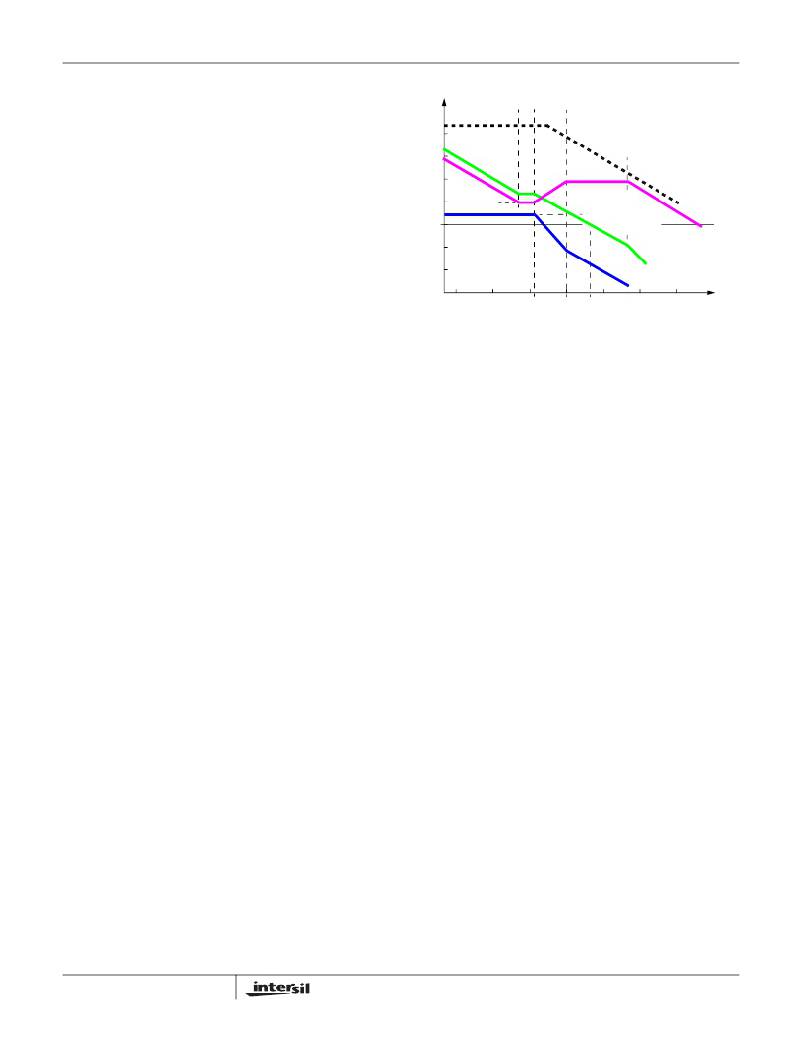

�F� Z1� F� Z2�

�F� P1�

�MODULATOR� GAIN�

�COMPENSATION GAIN�

�CLOSED� LOOP� GAIN�

�OPEN� LOOP� E/A� GAIN�

�F� P2�

�C� 3� =� -----------------------------------------------�

�20� log� ?� --------� ?�

�OSC�

�1�

�2� π� ?� R� 3� ?� 0.7� ?� f� SW�

�It� is� recommended� that� a� mathematical� model� is� used� to� plot�

�0�

�R2�

�?� R1� ?�

�d� MAX� ?� V� IN�

�20� log� ---------------------------------�

�V�

�G� FB�

�the� loop� response.� Check� the� loop� gain� against� the� error�

�amplifier� ’s� open-loop� gain.� Verify� phase� margin� results� and�

�adjust� as� necessary.� The� equations� in� Equation� 9,� describe�

�the� frequency� response� of� the� modulator� (G� MOD� ),� feedback�

�LOG�

�f� LC�

�f� CE�

�f� 0�

�G� CL�

�G� MOD�

�FREQUENCY�

�d� MAX� ?� V� IN� 1� +� s� (� f� )� ?� ESR� ?� C�

�G� MOD� (� f� )� =� ------------------------------� ?� -----------------------------------------------------------------------------------------------------------�

�G� FB� (� f� )� =� ----------------------------------------------------� ?�

�1� +� s� (� f� )� ?� (� R� 1� +� R� 3� )� ?� C� 3�

�(� 1� +� s� (� f� )� ?� R� 3� ?� C� 3� )� ?� ?� 1� +� s� (� f� )� ?� R� 2� ?� ?� ?� ?�

�?� ?� C� 1� ?� C� 2� ?� ?�

�compensation� (G� FB� )� and� closed-loop� response� (G� CL� ):�

�V� OSC� 1� +� s� (� f� )� ?� (� ESR� +� DCR� )� ?� C� +� s� (� f� )� ?� L� ?� C�

�1� +� s� (� f� )� ?� R� 2� ?� C� 1�

�s� (� f� )� ?� R� 1� ?� (� C� 1� +� C� 2� )�

�-------------------------------------------------------------------------------------------------------------------------�

�---------------------�

�?� ?� C� 1� +� C� 2� ?� ?�

�FIGURE� 10.� ASYMPTOTIC� BODE� PLOT� OF� CONVERTER� GAIN�

�frequencies� approaching� or� exceeding� half� the� switching�

�frequency.� When� designing� compensation� networks,� select�

�target� crossover� frequencies� in� the� range� of� 10%� to� 30%� of�

�the� switching� frequency,� f� SW� .�

�Component� Selection� Guidelines�

�Output� Capacitor� Selection�

�An� output� capacitor� is� required� to� filter� the� output� and� supply�

�G� CL� (� f� )� =� G� MOD� (� f� )� ?� G� FB� (� f� )�

�where� ,� s� (� f� )� =� 2� π� ?� f� ?� j�

�(EQ.� 9)�

�the� load� transient� current.� The� filtering� requirements� are� a�

�function� of� the� switching� frequency� and� the� ripple� current.�

�The� load� transient� requirements� are� a� function� of� the� slew�

�rate� (di/dt)� and� the� magnitude� of� the� transient� load� current.�

�COMPENSATION� BREAK� FREQUENCY� EQUATIONS�

�These� requirements� are� generally� met� with� a� mix� of�

�F� Z1� =� -------------------------------�

�F� P1� =� ---------------------------------------------�

�2� π� ?� R� 2� ?� ---------------------�

�F� Z2� =� -------------------------------------------------�

�F� P2� =� -------------------------------�

�1�

�2� π� ?� R� 2� ?� C� 1�

�1�

�2� π� ?� (� R� 1� +� R� 3� )� ?� C� 3�

�1�

�C� 1� ?� C� 2�

�C� 1� +� C� 2�

�1�

�2� π� ?� R� 3� ?� C� 3�

�capacitors� and� careful� layout.�

�Modern� microprocessors� produce� transient� load� rates� above�

�1A/ns.� High� frequency� capacitors� initially� supply� the� transient�

�and� slow� the� current� load� rate� seen� by� the� bulk� capacitors.�

�The� bulk� filter� capacitor� values� are� generally� determined� by�

�(EQ.� 10)�

�Figure� 10� shows� an� asymptotic� plot� of� the� DC/DC� converter’s�

�gain� vs� frequency.� The� actual� modulator� gain� has� a� high� gain�

�peak� dependent� on� the� quality� factor� (Q)� of� the� output� filter,�

�which� is� not� shown.� Using� the� above� guidelines� should� yield� a�

�compensation� gain� similar� to� the� curve� plotted.� The� open� loop�

�error� amplifier� gain� bounds� the� compensation� gain.� Check� the�

�compensation� gain� at� F� P2� against� the� capabilities� of� the� error�

�amplifier.� The� closed� loop� gain,� G� CL� ,� is� constructed� on� the�

�log-log� graph� of� Figure� 10� by� adding� the� modulator� gain,�

�G� MOD� (in� dB),� to� the� feedback� compensation� gain,� G� FB� (in�

�dB).� This� is� equivalent� to� multiplying� the� modulator� transfer�

�function� and� the� compensation� transfer� function� and� then�

�the� ESR� (effective� series� resistance)� and� voltage� rating�

�requirements� rather� than� actual� capacitance� requirements.�

�High� frequency� decoupling� capacitors� should� be� placed� as�

�close� to� the� power� pins� of� the� load� as� physically� possible.� Be�

�careful� not� to� add� inductance� in� the� circuit� board� wiring� that�

�could� cancel� the� usefulness� of� these� low� inductance�

�components.� Consult� with� the� manufacturer� of� the� load� on�

�specific� decoupling� requirements.� For� example,� Intel�

�recommends� that� the� high� frequency� decoupling� for� the�

�Pentium� Pro� be� composed� of� at� least� forty� (40)� 1.0mF�

�ceramic� capacitors� in� the� 1206� surface-mount� package.�

�Follow� on� specifications� have� only� increased� the� number�

�and� quality� of� required� ceramic� decoupling� capacitors.�

�plotting� the� resulting� gain.�

�Use� only� specialized� low-ESR� capacitors� intended� for�

�A� stable� control� loop� has� a� gain� crossing� with� close� to� a�

�-20dB/decade� slope� and� a� phase� margin� greater� than� +45°.�

�Include� worst� case� component� variations� when� determining�

�phase� margin.� The� mathematical� model� presented� makes� a�

�number� of� approximations� and� is� generally� not� accurate� at�

�12�

�switching-regulator� applications� for� the� bulk� capacitors.� The�

�bulk� capacitor’s� ESR� will� determine� the� output� ripple� voltage�

�and� the� initial� voltage� drop� after� a� high� slew-rate� transient.� An�

�aluminum� electrolytic� capacitor's� ESR� value� is� related� to� the�

�case� size� with� lower� ESR� available� in� larger� case� sizes.�

�FN6306.5�

�April� 15,� 2010�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL8105BIRZ-T | IC REG CTRLR BUCK PWM VM 10-DFN |

| B41041A6108M | 1000UF 50V 16X25 SINGLE END |

| ISL8105IRZ-T | IC REG CTRLR BUCK PWM VM 10-DFN |

| MC33164DM-3R2G | IC SENSOR UNDERVOLTAGE 8-MICRO |

| RBM28DSXH | CONN EDGECARD 56POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8105B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:+5V or +12V Single-Phase Synchronous Buck Converter PWM Controller with Integrated MOSFET Gate Drivers, Extended Soft-Start Time |

| ISL8105BCBZ | 功能描述:IC REG CTRLR BUCK PWM VM 8-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8105BCBZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 8-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:4,500 系列:PowerWise® PWM 型:控制器 输出数:1 频率 - 最大:1MHz 占空比:95% 电源电压:2.8 V ~ 5.5 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-40°C ~ 125°C 封装/外壳:6-WDFN 裸露焊盘 包装:带卷 (TR) 配用:LM1771EVAL-ND - BOARD EVALUATION LM1771 其它名称:LM1771SSDX |

| ISL8105BCRZ | 功能描述:IC REG CTRLR BUCK PWM VM 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8105BCRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 10-DFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 标准包装:4,500 系列:PowerWise® PWM 型:控制器 输出数:1 频率 - 最大:1MHz 占空比:95% 电源电压:2.8 V ~ 5.5 V 降压:是 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:无 工作温度:-40°C ~ 125°C 封装/外壳:6-WDFN 裸露焊盘 包装:带卷 (TR) 配用:LM1771EVAL-ND - BOARD EVALUATION LM1771 其它名称:LM1771SSDX |

发布紧急采购,3分钟左右您将得到回复。