参数资料

| 型号: | ISL98002CRZ-170 |

| 厂商: | Intersil |

| 文件页数: | 8/28页 |

| 文件大小: | 0K |

| 描述: | IC VID DIGITIZER 3CHN AFE 72-QFN |

| 标准包装: | 840 |

| 位数: | 8 |

| 通道数: | 3 |

| 功率(瓦特): | 535mW |

| 电压 - 电源,模拟: | 3 V ~ 3.6 V |

| 电压 - 电源,数字: | 3 V ~ 3.6 V |

| 封装/外壳: | 72-VFQFN 裸露焊盘 |

| 供应商设备封装: | 72-QFN(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

16

FN6535.1

December 7, 2009

Technical Highlights

The ISL98002 provides all the features of traditional triple

channel video AFEs, but adds several next-generation

enhancements, bringing performance and ease of use to

new levels.

DPLL

All video AFEs must phase lock to an HSYNC signal,

supplied either directly or embedded in the video stream

(Sync On Green). Historically, this has been implemented as

a traditional analog PLL. At SXGA and lower resolutions, an

analog PLL solution has proven adequate, if somewhat

troublesome (due to the need to adjust charge pump

currents, VCO ranges and other parameters to find the

optimum trade-off for a wide range of pixel rates).

As display resolutions and refresh rates have increased,

however, the pixel period has shrunk. An XGA pixel at a

60Hz refresh rate has 15.4ns to change and settle to its new

value. But at UXGA 75Hz, the pixel period is 4.9ns. Most

consumer graphics cards (even the ones with “350MHz”

DACs) spend most of that time slewing to the new pixel

value. The pixel may settle to its final value with 1ns or less

before it begins slewing to the next pixel. In many cases, it

rings and never settles at all. Thus precision, low-jitter

sampling is a fundamental requirement at these speeds, and

a difficult one for an analog PLL to meet.

The ISL98002's DPLL has less than 250ps of jitter,

peak-to-peak, and independent of the pixel rate. The DPLL

generates 64 phase steps per pixel (vs the industry standard

32), for fine, accurate positioning of the sampling point. The

crystal-locked NCO inside the DPLL completely eliminates

drift due to charge pump leakage, so there is inherently no

frequency or phase change across a line. An intelligent

all-digital loop filter/controller eliminates the need for the user

to have to program or change anything (except for the number

of pixels) to lock over a range from interlaced video (10MHz or

higher) to UXGA 60Hz (170MHz, with the ISL98002-170).

The DPLL eliminates much of the performance limitations and

complexity associated with noise-free digitization of high

speed signals.

Automatic Black Level Compensation (ABLC)

and Gain Control

Traditional video AFEs have an offset DAC prior to the ADC,

to both correct for offsets on the incoming video signals and

add/subtract an offset for user “brightness control” without

sacrificing the 8-bit dynamic range of the ADC. This solution

is adequate, but it places significant requirements on the

system's firmware, which must execute a loop that detects

the black portion of the signal and then serves the offset

DACs until that offset is nulled (or produces the desired ADC

output code). Once this has been accomplished, the offset

(both the offset in the AFE and the offset of the video card

generating the signal) is subject to drift (the temperature

inside a monitor or projector can easily change +50°C)

between power-on/offset calibration on a cold morning and

the temperature reached once the monitor and the monitor's

environment has reached a steady state. Offset can drift

significantly over +50°C, reducing image quality and

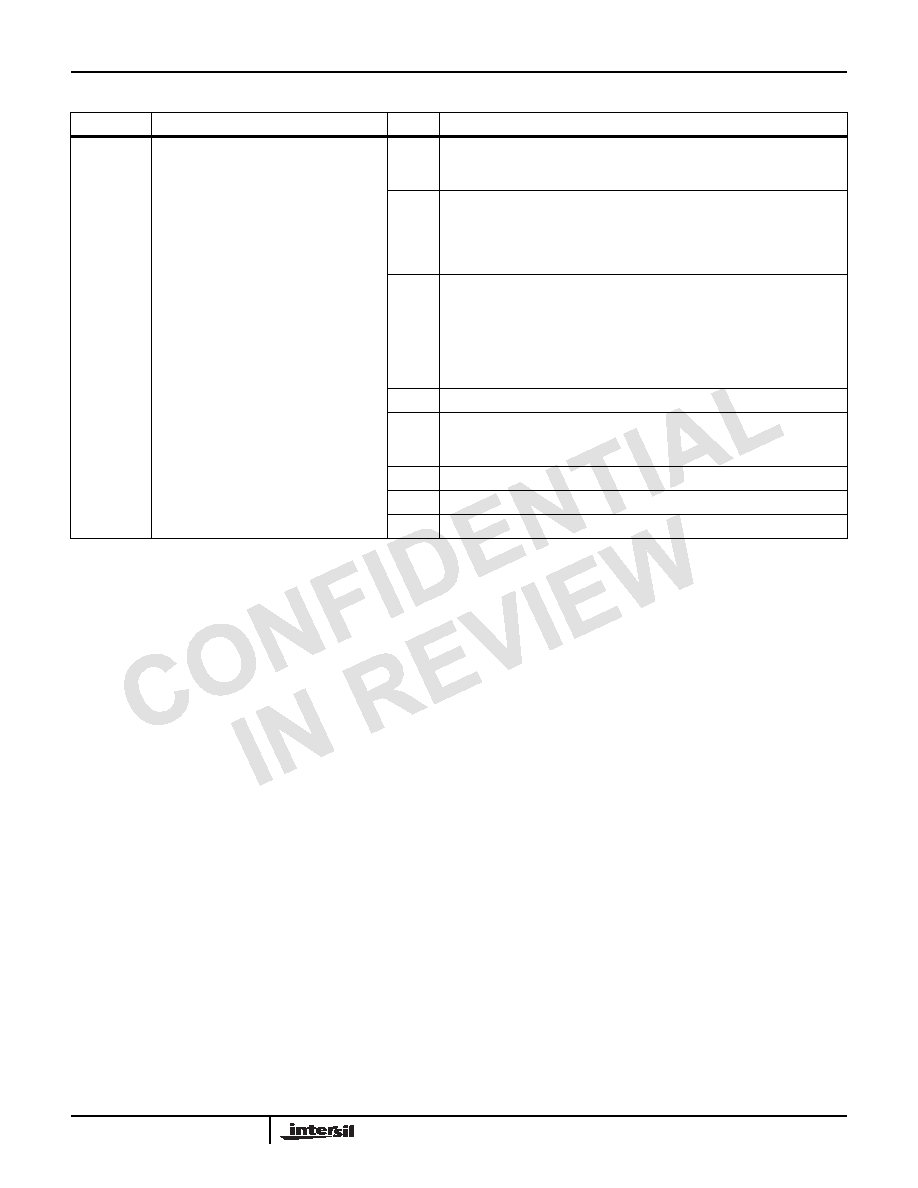

0x25

Sync Separator Control (0x00)

0

Three-state Sync

Outputs

0: VSYNCOUT, HSYNCOUT, HSOUT are active

(default)

1: VSYNCOUT, HSYNCOUT, HSOUT are in three-state

1

COAST Polarity

0: Coast active high (default)

1: Coast active low

Set to 0 for internal VSYNC extracted from CSYNC.

Set to 0 or 1 as appropriate to match external VSYNC

or external COAST.

2HSOUT Lock Edge

0: HSOUT's trailing edge is locked to selected

HSYNCIN's lock edge. Leading edge moves

backward in time as HSOUT width is increased

(X980xx default)

1: HSOUT's leading edge is locked to selected

HSYNCIN's lock edge. Trailing edge moves forward

in time as HSOUT width is increased

3

Reserved

Set to 0

4

VSYNCOUT Mode

0: VSYNCOUT is aligned to HSYNCOUT edge,

providing “perfect” VSYNC signal (default)

1: VSYNCOUT is “raw” integrator output

5

Reserved

Set to 0

6

Reserved

Set to 0

7

Reserved

Set to 0

Register Listing (Continued)

ADDRESS

REGISTER (DEFAULT VALUE)

BIT(S)

FUNCTION NAME

DESCRIPTION

ISL98002

相关PDF资料 |

PDF描述 |

|---|---|

| ISL98003CNZ-165 | IC AFE 3CH 8BIT 165MHZ 80EPTQFP |

| ISLA118P50IRZ | IC ADC 8BIT SPI/SRL 500M 72QFN |

| ISLA212P20IRZ | IC ADC 12BIT SRL/SPI 72QFN |

| ISLA214S50IR1Z | IC ADC |

| ISLA222P13IRZ | IC ADC 12BIT SRL/SPI 72QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL98002CRZ-EVALZ | 功能描述:EVAL BOARD FOR ISL98002CRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ISL98003CNZ-110 | 功能描述:IC AFE 3CH 8BIT 110MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003CNZ-150 | 功能描述:IC AFE 3CH 8BIT 150MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003CNZ-165 | 功能描述:IC AFE 3CH 8BIT 165MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003CNZ-165S2733 | 制造商:Intersil Corporation 功能描述:TANGTOP ISL98003CNZ-T165 W/BUSINESS TRACKING REQUIREMENTS - Trays |

发布紧急采购,3分钟左右您将得到回复。