- 您现在的位置:买卖IC网 > PDF目录239729 > IV80C52EXXX-25:RD (ATMEL CORP) 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | IV80C52EXXX-25:RD |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | 1.40 MM HEIGHT, VQFP-44 |

| 文件页数: | 30/134页 |

| 文件大小: | 3805K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页

125

8011Q–AVR–02/2013

ATmega164P/324P/644P

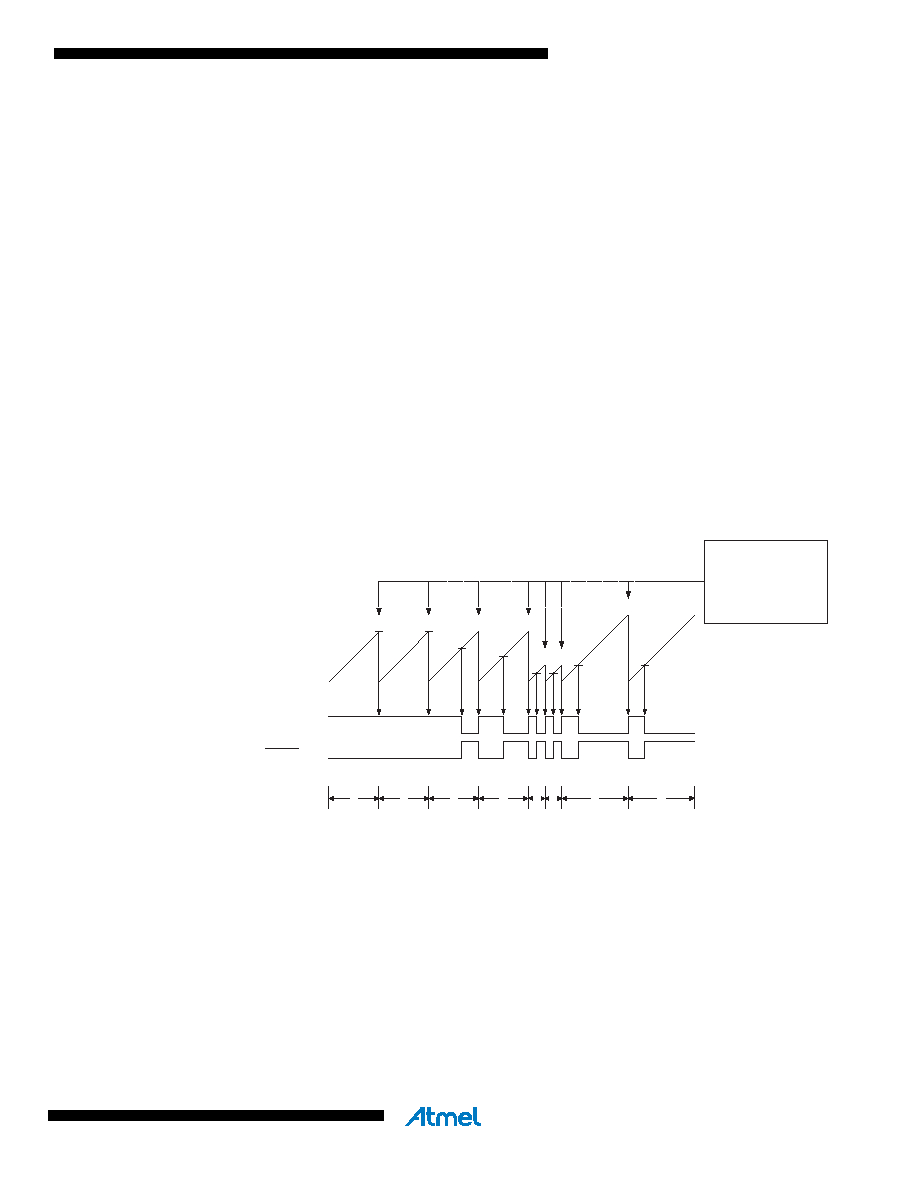

rect and phase and frequency correct PWM modes that use dual-slope operation. This high

frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC

applications. High frequency allows physically small sized external components (coils, capaci-

tors), hence reduces total system cost.

The PWM resolution for fast PWM can be fixed to 8-bit, 9-bit, or 10-bit, or defined by either ICRn

or OCRnA. The minimum resolution allowed is 2-bit (ICRn or OCRnA set to 0x0003), and the

maximum resolution is 16-bit (ICRn or OCRnA set to MAX). The PWM resolution in bits can be

calculated by using the following equation:

In fast PWM mode the counter is incremented until the counter value matches either one of the

fixed values 0x00FF, 0x01FF, or 0x03FF (WGMn3:0 = 5, 6, or 7), the value in ICRn (WGMn3:0 =

14), or the value in OCRnA (WGMn3:0 = 15). The counter is then cleared at the following timer

clock cycle. The timing diagram for the fast PWM mode is shown in Figure 13-7. The figure

shows fast PWM mode when OCRnA or ICRn is used to define TOP. The TCNTn value is in the

timing diagram shown as a histogram for illustrating the single-slope operation. The diagram

includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNTn

slopes represent compare matches between OCRnx and TCNTn. The OCnx Interrupt Flag will

be set when a compare match occurs.

Figure 13-7. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOVn) is set each time the counter reaches TOP. In addition

the OCnA or ICFn Flag is set at the same timer clock cycle as TOVn is set when either OCRnA

or ICRn is used for defining the TOP value. If one of the interrupts are enabled, the interrupt han-

dler routine can be used for updating the TOP and compare values.

When changing the TOP value the program must ensure that the new TOP value is higher or

equal to the value of all of the Compare Registers. If the TOP value is lower than any of the

Compare Registers, a compare match will never occur between the TCNTn and the OCRnx.

Note that when using fixed TOP values the unused bits are masked to zero when any of the

OCRnx Registers are written.

The procedure for updating ICRn differs from updating OCRnA when used for defining the TOP

value. The ICRn Register is not double buffered. This means that if ICRn is changed to a low

R

FPWM

TOP

1

+

log

2

log

-----------------------------------

=

TCNTn

OCRnx/TOP Update and

TOVn Interrupt Flag Set and

OCnA Interrupt Flag Set

or ICFn Interrupt Flag Set

(Interrupt on TOP)

1

7

Period

2

3

4

5

6

8

OCnx

(COMnx1:0 = 2)

(COMnx1:0 = 3)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT75T43100S66BS | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA304 |

| IDT79RC64T575250DPI | 64-BIT, 250 MHz, RISC PROCESSOR, PQFP208 |

| IDT79R3081-40DL8 | 32-BIT, 40 MHz, RISC PROCESSOR, PQCC84 |

| ICS84325EM | 250 MHz, OTHER CLOCK GENERATOR, PDSO24 |

| ICS84427BM | 625 MHz, OTHER CLOCK GENERATOR, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IV-811MX | 制造商:Digital ID View 功能描述:8 CH H.264 DVR USB REMOTENO HDD 制造商:DIGITAL IDVIEW 功能描述:8 CH H.264 DVR USB REMOTE NO HDD |

| IV-811Z-960H-1000 | 制造商:Digital ID View 功能描述:8-Channel 960H i-Cloud Series DVR with 1TB HDD |

| IV-811Z-960H-500 | 制造商:Digital ID View 功能描述:8-Channel 960H i-Cloud Series DVR with 500GB HDD 制造商:DIGITAL IDVIEW 功能描述:8-CHNL ICLOUD 960H DVR 500GB HDD HDMI OUT |

| IV-811ZAECO-1000 | 制造商:Digital ID View 功能描述:8 Ch H.264 DVR D1 1Tbb Dvd |

| IV-811ZAECO-500 | 制造商:Digital ID View 功能描述:8 Ch H.264 DVR D1 500GB Dvd |

发布紧急采购,3分钟左右您将得到回复。