- 您现在的位置:买卖IC网 > PDF目录299245 > K7A163280A-QI16 512K X 32 CACHE SRAM, 3.5 ns, PQFP100 PDF资料下载

参数资料

| 型号: | K7A163280A-QI16 |

| 元件分类: | SRAM |

| 英文描述: | 512K X 32 CACHE SRAM, 3.5 ns, PQFP100 |

| 封装: | 14 X 20 MM, TQFP-100 |

| 文件页数: | 9/18页 |

| 文件大小: | 473K |

| 代理商: | K7A163280A-QI16 |

512Kx36/x32 & 1Mx18 Synchronous SRAM

- 17 -

Rev 0.2

Dec 2001

K7A161880A

K7A163280A

Preliminary

K7A163680A

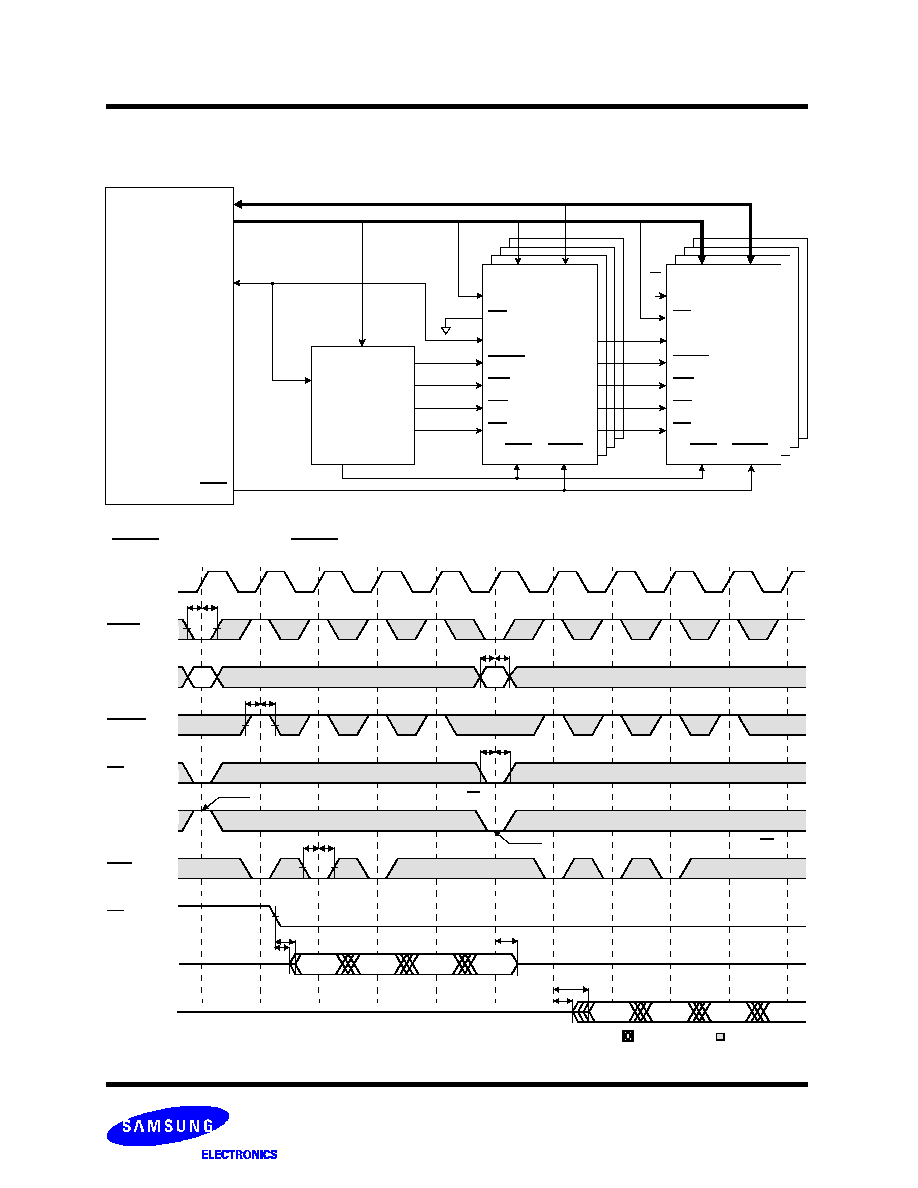

APPLICATION INFORMATION

DEPTH EXPANSION

Data

Address

CLK

ADS

Microprocessor

CS2

CLK

ADSC

WEx

OE

CS1

Address Data

ADV

ADSP

1Mx18

SPB

SRAM

(Bank 0)

CS2

CLK

ADSC

WEx

OE

CS1

Address Data

ADV

ADSP

1Mx18

SPB

SRAM

(Bank 1)

CLK

Address

Cache

Controller

A[0:20]

A[20]

A[0:19]

A[20]

A[0:19]

I/O[0:71]

Clock

ADSP

ADDRESS

Data Out

Bank 0 is selected by CS2, and Bank 1 deselected by CS2

Q1-1

Q1-2

Q1-4

Q1-3

OE

Data Out

tSS

tSH

Don

′t Care

A1

A2

WRITE

CS1

An+1

ADV

(Bank 0)

(Bank 1)

Q2-2

Q2-4

Q2-3

tAS

tAH

tWS

tWH

tADVS

tADVH

tOE

tLZOE

tHZC

Bank 0 is deselected by CS2, and Bank 1 selected by CS2

tCSS

tCSH

tCD

tLZC

[0:n]

Undefined

Q2-1

INTERLEAVE READ TIMING (Refer to non-interleave write timing for interleave write timing)

(ADSP CONTROLLED , ADSC=HIGH)

The Samsung 1Mx18 Synchronous Pipelined Burst SRAM has two additional chip selects for simple depth expansion.

This permits easy secondary cache upgrades from 1M depth to 2M depth without extra logic.

*Notes : n = 14 32K depth ,

15 64K depth

16 128K depth ,

17 256K depth

18 512K depth ,

19 1M depth

20 2M depth

相关PDF资料 |

PDF描述 |

|---|---|

| K7A403601A-QC140 | 128K X 36 CACHE SRAM, 4 ns, PQFP100 |

| K85X-AA-15P-K30 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER, PLUG |

| K85X-AA-15P-KJ15 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER, PLUG |

| K85X-AA-15P-KJ30 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER, PLUG |

| K85X-AA-15P-KJ | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR, SOLDER, PLUG |

相关代理商/技术参数 |

参数描述 |

|---|---|

| K7A163600A | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 Synchronous SRAM |

| K7A163600AQC14 | 制造商:Samsung Semiconductor 功能描述: |

| K7A163600A-QC16000 | 制造商:Samsung Semiconductor 功能描述: |

| K7A163600A-QC25000 | 制造商:Samsung Semiconductor 功能描述: |

| K7A163600MQC14 | 制造商:Samsung Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。