- 您现在的位置:买卖IC网 > PDF目录22054 > KMC8144TVT1000A (Freescale Semiconductor)IC DSP 783FCPBGA PDF资料下载

参数资料

| 型号: | KMC8144TVT1000A |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 36/80页 |

| 文件大小: | 0K |

| 描述: | IC DSP 783FCPBGA |

| 标准包装: | 2 |

| 系列: | StarCore |

| 类型: | SC3400 内核 |

| 接口: | EBI/EMI,以太网,I²C,PCI,Serial RapidIO,SPI,TDM,UART,UTOPIA |

| 时钟速率: | 1.0GHz |

| 非易失内存: | ROM(96 kB) |

| 芯片上RAM: | 10.5MB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.00V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 783-BBGA,FCBGA |

| 供应商设备封装: | 783-FCPBGA(29x29) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

�� �

�

Electrical� Characteristics�

�2.6.3�

�Reset� Timing�

�The� MSC8144� has� several� inputs� to� the� reset� logic:�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�?�

�Power-on� reset� (� PORESET� )�

�External� hard� reset� (� HRESE� T� )�

�External� soft� reset� (� SRESET� )�

�Software� watchdog� reset�

�JTAG� reset�

�RapidIO� reset�

�Software� hard� reset�

�Software� soft� reset�

�All� MSC8144� reset� sources� are� fed� into� the� reset� controller,� which� takes� different� actions� depending� on� the� source� of� the� reset.�

�The� reset� status� register� indicates� the� most� recent� sources� to� cause� a� reset.� Table� 17� describes� the� reset� sources.�

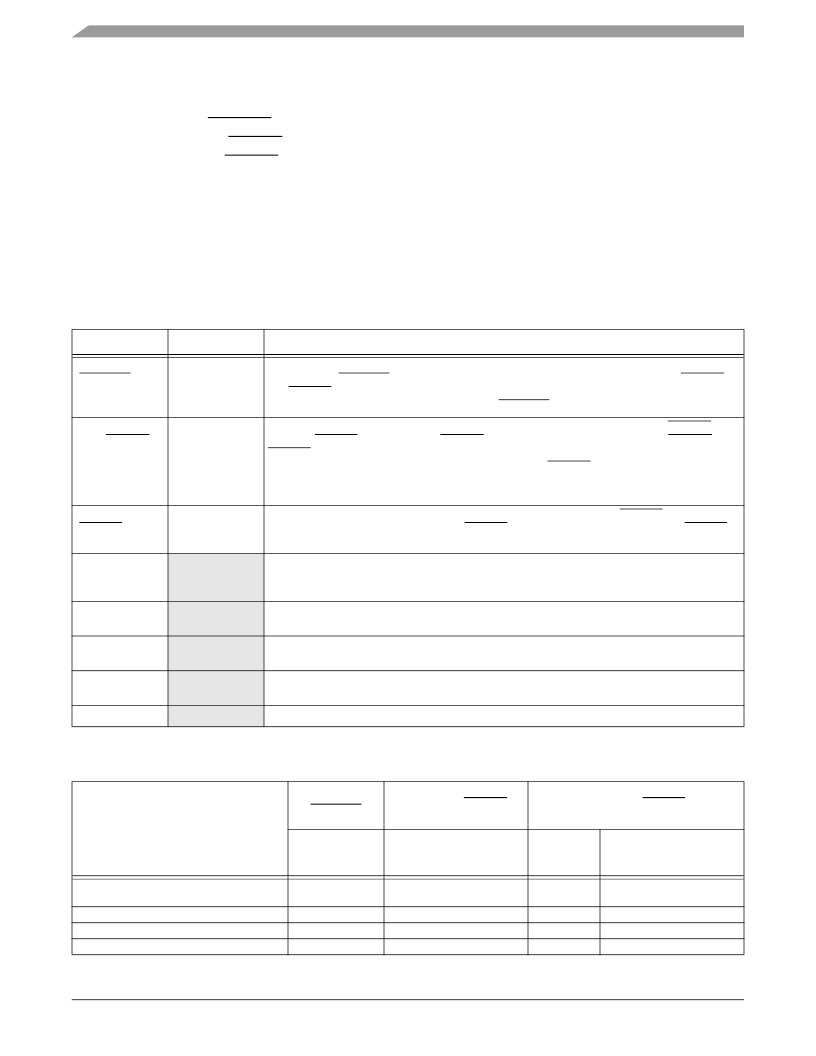

�Table� 17.� Reset� Sources�

�Name�

�Power-on� reset�

�(PORESET)�

�External� hard�

�reset� (HRESET)�

�External� soft� reset�

�(SRESET)�

�Host� reset�

�command� through�

�the� TAP�

�Software�

�watchdog� reset�

�RapidIO� reset�

�Software� hard�

�reset�

�Software� soft� reset�

�Direction�

�Input�

�Input/� Output�

�Input/� Output�

�Internal�

�Internal�

�Internal�

�Internal�

�Internal�

�Description�

�Initiates� the� power-on� reset� flow� that� resets� the� MSC8144� and� configures� various� attributes� of� the�

�MSC8144.� On� PORESET,� the� entire� MSC8144� device� is� reset.� All� PLLs� states� is� reset,� HRESET�

�and� SRESET� are� driven,� the� extended� cores� are� reset, and� system� configuration� is� sampled.� The�

�reset� source� and� word� are� configured� only� when� PORESET� is� asserted.�

�Initiates� the� hard� reset� flow� that� configures� various� attributes� of� the� MSC8144.� While� HRESET� is�

�asserted� ,� SRESET� is� also� asserted.� HRESET� is� an� open-drain� pin.� Upon� hard� reset,� HRESET� and�

�SRESET� are� driven,� the� extended� cores� are� reset,� and� system� configuration� is� sampled.� Note� that�

�the� RCW� (reset� Configuration� Word)� is� not� reloaded� during� HRESET� assertion� after� out� of� power� on�

�reset� sequence.� The� reset� configuration� word� is� described� in� the� Reset� chapter� in� the� MSC8144�

�Reference� Manual� .�

�Initiates� the� soft� reset� flow.� The� MSC8144� detects� an� external� assertion� of� SRESET� only� if� it� occurs�

�while� the� MSC8144� is� not� asserting� reset.� SRESET� is� an� open-drain� pin.� Upon� soft� reset,� SRESET� is�

�driven,� the� extended� cores� are� reset,� and� system� configuration� is� maintained.�

�When� a� host� reset� command� is� written� through� the� Test� Access� Port� (TAP),� the� TAP� logic� asserts� the�

�soft� reset� signal� and� an� internal� soft� reset� sequence� is� generated.�

�When� the� MSC8144� watchdog� count� reaches� zero,� a� software� watchdog� reset� is� signalled.� The�

�enabled� software� watchdog� event� then� generates� an� internal� hard� reset� sequence.�

�When� the� RapidIO� logic� asserts� the� RapidIO� hard� reset� signal,� it� generates� an� internal� hard� reset�

�sequence.�

�A� hard� reset� sequence� can� be� initialized� by� writing� to� a� memory� mapped� register� (RCR)�

�A� soft� reset� sequence� can� be� initialized� by� writing� to� a� memory� mapped� register� (RCR)�

�Table� 18� summarizes� the� reset� actions� that� occur� as� a� result� of� the� different� reset� sources.�

�Table� 18.� Reset� Actions� for� Each� Reset� Source�

�Reset� Action/Reset� Source�

�Power-On� Reset�

�(PORESET)�

�Hard� Reset� (HRESET)�

�Soft� Reset� (SRESET)�

�External� or� Internal�

�External� or�

�JTAG� Command:�

�External� only�

�(Software� Watchdog,�

�Software� or� RapidIO)�

�internal�

�Software�

�EXTEST,� CLAMP,� or�

�HIGHZ�

�Configuration� pins� sampled� (Refer� to�

�Yes�

�No�

�No�

�No�

��PLL� state� reset�

�Select� reset� configuration� source�

�System� reset� configuration� write�

�Yes�

�Yes�

�Yes�

�No�

�No�

�No�

�No�

�No�

�No�

�No�

�No�

�No�

�MSC8144� Quad� Core� Digital� Signal� Processor� Data� Sheet,� Rev.� 16�

�36�

�Freescale� Semiconductor�

�相关PDF资料 |

PDF描述 |

|---|---|

| KMC8144VT1000A | IC DSP 783FCPBGA |

| TPSD106M035S0300 | CAP TANT 10UF 35V 20% 2917 |

| KMC8144TVT800B | IC DSP 783FCPBGA |

| F931C105MAA | CAP TANT 1UF 16V 20% 1206 |

| KMC8144TVT800A | IC DSP 783FCPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KMC8144TVT1000B | 功能描述:IC DSP 783FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| KMC8144TVT800A | 功能描述:数字信号处理器和控制器 - DSP, DSC PACSUN SAMPLE PART RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| KMC8144TVT800B | 功能描述:IC DSP 783FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| KMC8144VT1000A | 功能描述:数字信号处理器和控制器 - DSP, DSC PACSUN SAMPLE PART RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| KMC8144VT1000B | 功能描述:IC DSP 783FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

发布紧急采购,3分钟左右您将得到回复。