- 您现在的位置:买卖IC网 > PDF目录22053 > KMC8144VT800B (Freescale Semiconductor)IC DSP 783FCPBGA PDF资料下载

参数资料

| 型号: | KMC8144VT800B |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 43/80页 |

| 文件大小: | 0K |

| 描述: | IC DSP 783FCPBGA |

| 标准包装: | 2 |

| 系列: | StarCore |

| 类型: | SC3400 内核 |

| 接口: | EBI/EMI,以太网,I²C,PCI,Serial RapidIO,SPI,TDM,UART,UTOPIA |

| 时钟速率: | 800MHz |

| 非易失内存: | ROM(96 kB) |

| 芯片上RAM: | 10.5MB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.00V |

| 工作温度: | 0°C ~ 90°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 783-BBGA,FCBGA |

| 供应商设备封装: | 783-FCPBGA(29x29) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

�� �

�

Electrical� Characteristics�

�Using� these� waveforms,� the� definitions� are� as� follows:�

�1.�

�2.�

�3.�

�4.�

�5.�

�6.�

�The� transmitter� output� signals� and� the� receiver� input� signals� TD,� TD,� RD� and� RD� each� have� a� peak-to-peak� voltage�

�(V� PP� )� swing� of� A� –� B.�

�The� differential� output� signal� of� the� transmitter,� V� OD� ,� is� defined� as� V� TD� –� V� TD� .�

�The� differential� input� signal� of� the� receiver,� V� ID� ,� is� defined� as� V� RD� –� V� RD� .�

�The� differential� output� signal� of� the� transmitter� and� the� differential� input� signal� of� the� receiver� each� range� from� A� –� B�

�to� –(A� –� B).�

�The� peak� value� of� the� differential� transmitter� output� signal� and� the� differential� receiver� input� signal� is� A� –� B.�

�The� value� of� the� differential� transmitter� output� signal� and� the� differential� receiver� input� signal� is� 2� ×� (A� –� B)� V� PP� .�

�To� illustrate� these� definitions� using� real� values,� consider� the� case� of� a� CML� (Current� Mode� Logic)� transmitter� that� has� a� common�

�mode� voltage� of� 2.25� V� and� each� of� its� outputs,� TD� and� TD,� has� a� swing� that� goes� between� 2.5� V� and� 2.0� V.� Using� these� values,�

�the� peak-to-peak� voltage� swing� of� the� signals� TD� and� TD� is� 500� mV� PP� .� The� differential� output� signal� ranges� between� 500� mV�

�and� –500� mV.� The� peak� differential� voltage� is� 500� mV.� The� peak-to-peak� differential� voltage� is� 1000� mV� PP� .�

�Note:�

�AC� electrical� specifications� are� given� for� transmitter� and� receiver.� Long� run� and� short� run� interfaces� at� three� baud�

�rates� (a� total� of� six� cases)� are� described.� The� parameters� for� the� AC� electrical� specifications� are� guided� by� the� XAUI�

�electrical� interface� specified� in� Clause� 47� of� IEEE?� Std� 802.3ae-2002?.� XAUI� has� similar� application� goals� to�

�serial� RapidIO.� The� goal� of� this� standard� is� that� electrical� designs� for� serial� RapidIO� can� reuse� electrical� designs� for�

�XAUI,� suitably� modified� for� applications� at� the� baud� intervals� and� reaches� described� herein.�

�2.6.5.3�

�Equalization�

�With� the� use� of� high� speed� serial� links,� the� interconnect� media� will� cause� degradation� of� the� signal� at� the� receiver.� Effects� such�

�as� Inter-Symbol� Interference� (ISI)� or� data� dependent� jitter� are� produced.� This� loss� can� be� large� enough� to� degrade� the� eye�

�opening� at� the� receiver� beyond� what� is� allowed� in� the� specification.� To� negate� a� portion� of� these� effects,� equalization� can� be�

�used.� The� most� common� equalization� techniques� that� can� be� used� are:�

�?�

�?�

�A� passive� high� pass� filter� network� placed� at� the� receiver.� This� is� often� referred� to� as� passive� equalization.�

�The� use� of� active� circuits� in� the� receiver.� This� is� often� referred� to� as� adaptive� equalization.�

�2.6.5.4�

�Transmitter� Specifications�

�LP-Serial� transmitter� electrical� and� timing� specifications� are� stated� in� the� text� and� tables� of� this� section.� The� differential� return�

�loss,� S11,� of� the� transmitter� in� each� case� shall� be� better� than�

�?�

�?�

�–10� dB� for� (baud� frequency)/10� <� freq(f)� <� 625� MHz,� and�

�–10� dB� +� 10log(f/625� MHz)� dB� for� 625� MHz� ≤� freq(f)� ≤� baud� frequency�

�The� reference� impedance� for� the� differential� return� loss� measurements� is� 100� Ω� resistive.� Differential� return� loss� includes�

�contributions� from� internal� circuitry,� packaging,� and� any� external� components� related� to� the� driver.� The� output� impedance�

�requirement� applies� to� all� valid� output� levels.� It� is� recommended� that� the� 20–80%� rise/fall� time� of� the� transmitter,� as� measured�

�at� the� transmitter� output,� have� a� minimum� value� 60� ps� in� each� case.� It� is� also� recommended� that� the� timing� skew� at� the� output�

�of� an� LP-Serial� transmitter� between� the� two� signals� comprising� a� differential� pair� not� exceed� 25� ps� at� 1.25� GB,� 20� ps� at� 2.50�

�GB,� and� 15� ps� at� 3.125� GB.�

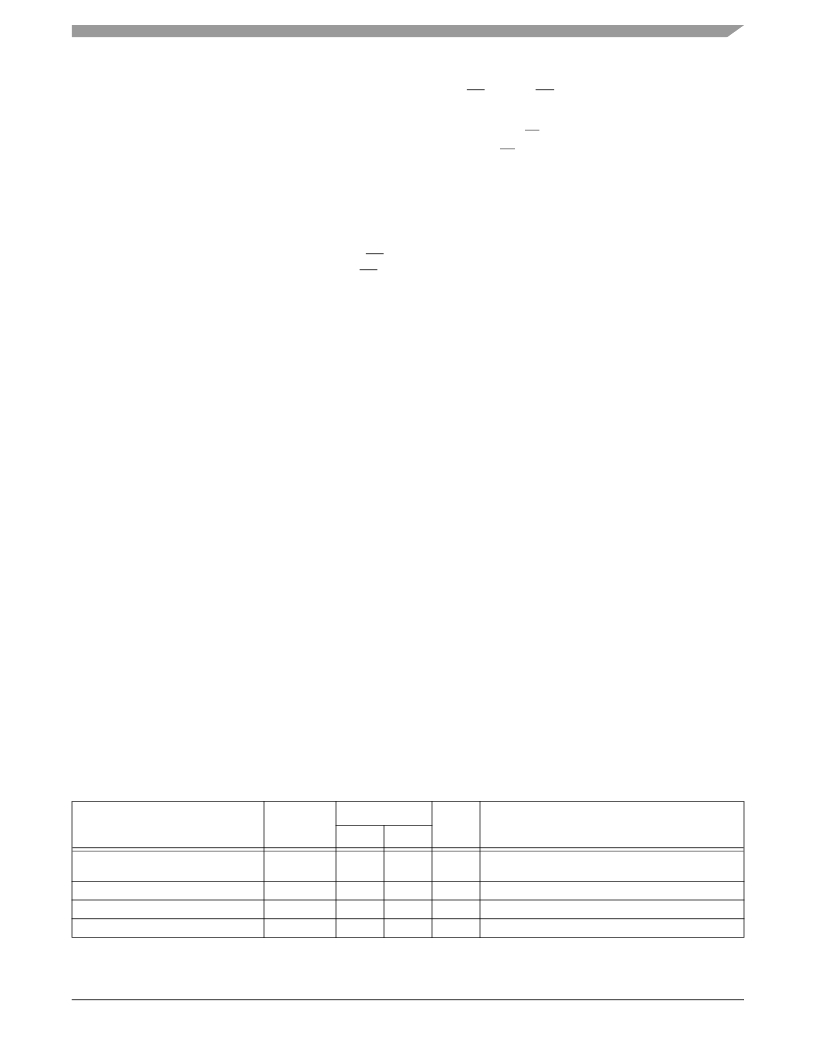

�Table� 25.� Short� Run� Transmitter� AC� Timing� Specifications—1.25� GBaud�

�Range�

�Characteristic�

�Symbol�

�Min�

�Max�

�Unit�

�Notes�

�Output� Voltage�

�V� O�

�–0.40�

�2.30�

�V�

�Voltage� relative� to� COMMON� of� either� signal�

�comprising� a� differential� pair�

�Differential� Output� Voltage�

�Deterministic� Jitter�

�Total� Jitter�

�V� DIFFPP�

�J� D�

�J� T�

�500�

�1000�

�0.17�

�0.35�

�mV� PP�

�UI� PP�

�UI� PP�

�MSC8144� Quad� Core� Digital� Signal� Processor� Data� Sheet,� Rev.� 16�

�Freescale� Semiconductor�

�43�

�相关PDF资料 |

PDF描述 |

|---|---|

| TAJC686K010ANJ | CAP TANT 68UF 10V 10% 2312 |

| KMC8144VT800A | IC DSP 783FCPBGA |

| KMC8144VT1000B | IC DSP 783FCPBGA |

| GEC10DRTN-S734 | CONN EDGECARD 20POS DIP .100 SLD |

| B82496C3181J | INDUCTOR 180NH .12A 0603 5% |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KMC8358CVVAGDGA | 功能描述:微处理器 - MPU 8360 TBGA C NONENC NO-PB RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| KMC8358CZUAGDGA | 功能描述:微处理器 - MPU 8360 TBGA C NON-ENCRP RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| KMC8358ECVRAGDDA | 功能描述:微处理器 - MPU 8358 PBGA ENCRP NO-PB RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| KMC8358ECVRAGDGA | 功能描述:微处理器 - MPU 8358 PBGA ENCRP NO-PB RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| KMC8358ECVVAGDGA | 功能描述:微处理器 - MPU 8360 TBGA C ENC NO-PB RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

发布紧急采购,3分钟左右您将得到回复。