- 您现在的位置:买卖IC网 > PDF目录11595 > KSZ8851-16MLLI (Micrel Inc)IC MAC CTLR 1PORT W/BUS 48-TQFP PDF资料下载

参数资料

| 型号: | KSZ8851-16MLLI |

| 厂商: | Micrel Inc |

| 文件页数: | 68/84页 |

| 文件大小: | 0K |

| 描述: | IC MAC CTLR 1PORT W/BUS 48-TQFP |

| 标准包装: | 250 |

| 控制器类型: | 以太网控制器,MAC/PHY |

| 接口: | 总线 |

| 电源电压: | 1.8V,2.5V,3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 1081 (CN2011-ZH PDF) |

| 其它名称: | 576-3505 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

PIC16F7X

DS30325B-page 68

2002 Microchip Technology Inc.

9.3.2

MASTER MODE

Master mode of operation is supported in firmware

using interrupt generation on the detection of the

START and STOP conditions. The STOP (P) and

START (S) bits are cleared from a RESET or when the

SSP module is disabled. The STOP (P) and START (S)

bits will toggle based on the START and STOP condi-

tions. Control of the I2C bus may be taken when the P

bit is set, or the bus is IDLE and both the S and P bits

are clear.

In Master mode, the SCL and SDA lines are manipu-

lated by clearing the corresponding TRISC<4:3> bit(s).

The output level is always low, irrespective of the

value(s) in PORTC<4:3>. So when transmitting data, a

’1’ data bit must have the TRISC<4> bit set (input) and

a ’0’ data bit must have the TRISC<4> bit cleared (out-

put). The same scenario is true for the SCL line with the

TRISC<3> bit. Pull-up resistors must be provided

externally to the SCL and SDA pins for proper opera-

tion of the I2C module.

The following events will cause SSP Interrupt Flag bit,

SSPIF, to be set (SSP Interrupt will occur if enabled):

START condition

STOP condition

Data transfer byte transmitted/received

Master mode of operation can be done with either the

Slave mode IDLE (SSPM3:SSPM0 = 1011), or with the

Slave active. When both Master and Slave modes are

enabled, the software needs to differentiate the

source(s) of the interrupt.

9.3.3

MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the

detection of the START and STOP conditions, allows

the determination of when the bus is free. The STOP

(P) and START (S) bits are cleared from a RESET or

when the SSP module is disabled. The STOP (P) and

START (S) bits will toggle based on the START and

STOP conditions. Control of the I2C bus may be taken

when bit P (SSPSTAT<4>) is set, or the bus is IDLE

and both the S and P bits clear. When the bus is busy,

enabling the SSP Interrupt will generate the interrupt

when the STOP condition occurs.

In Multi-Master operation, the SDA line must be moni-

tored to see if the signal level is the expected output

level. This check only needs to be done when a high

level is output. If a high level is expected and a low level

is present, the device needs to release the SDA and

SCL lines (set TRISC<4:3>). There are two stages

where this arbitration can be lost, these are:

Address Transfer

Data Transfer

When the slave logic is enabled, the slave continues to

receive. If arbitration was lost during the address trans-

fer stage, communication to the device may be in

progress. If addressed, an ACK pulse will be gener-

ated. If arbitration was lost during the data transfer

stage, the device will need to retransfer the data at a

later time.

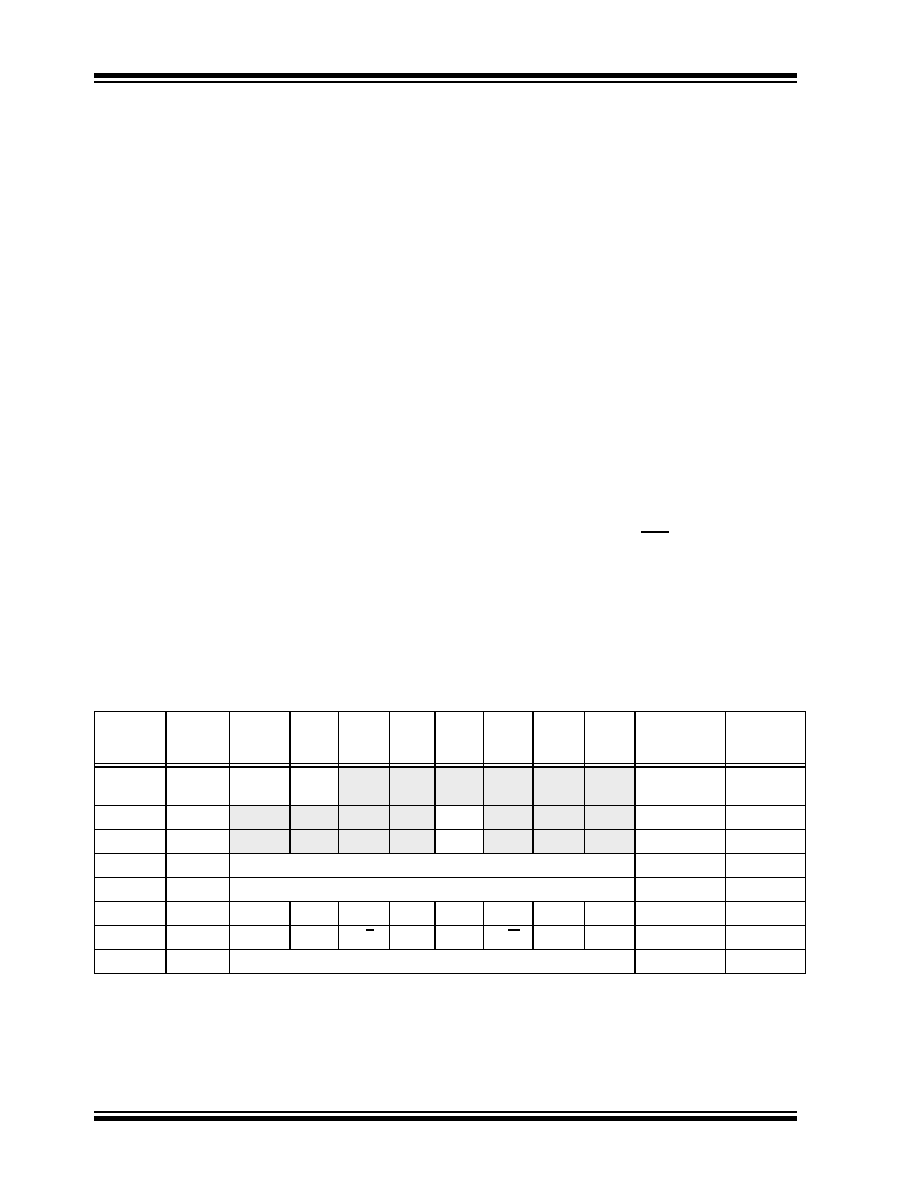

TABLE 9-3:

REGISTERS ASSOCIATED WITH I2C OPERATION

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on:

POR,

BOR

Value on

all other

RESETS

0Bh, 8Bh,

10Bh,18Bh

INTCON

GIE

PEIE

TMR0IE

INTE

RBIE

TMR0IF

INTF

RBIF

0000 000x

0000 000u

0Ch

PIR1

PSPIF(1)

ADIF

RCIF

TXIF

SSPIF CCP1IF TMR2IF TMR1IF

0000 0000

8Ch

PIE1

PSPIE(1)

ADIE

RCIE

TXIE

SSPIE CCP1IE TMR2IE TMR1IE

0000 0000

13h

SSPBUF

Synchronous Serial Port Receive Buffer/Transmit Register

xxxx xxxx

uuuu uuuu

93h

SSPADD

Synchronous Serial Port (I2C mode) Address Register

0000 0000

14h

SSPCON

WCOL

SSPOV SSPEN

CKP

SSPM3 SSPM2 SSPM1 SSPM0

0000 0000

94h

SSPSTAT

SMP(2)

CKE(2)

D/A

PS

R/W

UA

BF

0000 0000

87h

TRISC

PORTC Data Direction Register

1111 1111

Legend:

x

= unknown, u = unchanged, - = unimplemented locations read as ’0’. Shaded cells are not used by SSP module in I2C mode.

Note

1: PSPIF and PSPIE are reserved on the PIC16F73/76; always maintain these bits clear.

2: Maintain these bits clear in I2C mode.

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8851-16MLL | IC CTLR MAC/PHY NON-PCI 48-LQFP |

| KSZ8873RLL | IC ETHERNET SWITCH 3PORT 64-LQFP |

| KSZ8851-16MQLI | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| KSZ8851-16MQL | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| LTC4278CDKD#PBF | IC PD IEEE 802.3AT 25.5W 32-DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8851-16MLLI TR | 功能描述:以太网 IC 10/100BT Ethernet MAC + PHY with Generic (8, 16-bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLJ | 功能描述:以太网 IC Single-Port Ethernet MAC Controller with 8/16-Bit Non-PCI Interface (125C support) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLJ_10 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:Single-Port Ethernet MAC Controller with 8-Bit or 16-Bit Non-PCI Interface |

| KSZ8851-16MLLU | 功能描述:以太网 IC Single-Port Ethernet Controller (Automotive Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLU TR | 功能描述:以太网 IC Single-Port Ethernet Controller (Automotive Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。