- 您现在的位置:买卖IC网 > PDF目录11595 > KSZ8851-16MLLI (Micrel Inc)IC MAC CTLR 1PORT W/BUS 48-TQFP PDF资料下载

参数资料

| 型号: | KSZ8851-16MLLI |

| 厂商: | Micrel Inc |

| 文件页数: | 73/84页 |

| 文件大小: | 0K |

| 描述: | IC MAC CTLR 1PORT W/BUS 48-TQFP |

| 标准包装: | 250 |

| 控制器类型: | 以太网控制器,MAC/PHY |

| 接口: | 总线 |

| 电源电压: | 1.8V,2.5V,3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 1081 (CN2011-ZH PDF) |

| 其它名称: | 576-3505 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页当前第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

2002 Microchip Technology Inc.

DS30325B-page 73

PIC16F7X

10.2

USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-

zero (NRZ) format (one START bit, eight or nine data

bits, and one STOP bit). The most common data format

is 8-bits. An on-chip, dedicated, 8-bit baud rate gener-

ator can be used to derive standard baud rate frequen-

cies from the oscillator. The USART transmits and

receives the LSb first. The USART’s transmitter and

receiver are functionally independent, but use the

same data format and baud rate. The baud rate gener-

ator produces a clock, either x16 or x64 of the bit shift

rate, depending on bit BRGH (TXSTA<2>). Parity is not

supported by the hardware, but can be implemented in

software (and stored as the ninth data bit). Asynchro-

nous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC

(TXSTA<4>).

The USART Asynchronous module consists of the fol-

lowing important elements:

Baud Rate Generator

Sampling Circuit

Asynchronous Transmitter

Asynchronous Receiver

10.2.1

USART ASYNCHRONOUS

TRANSMITTER

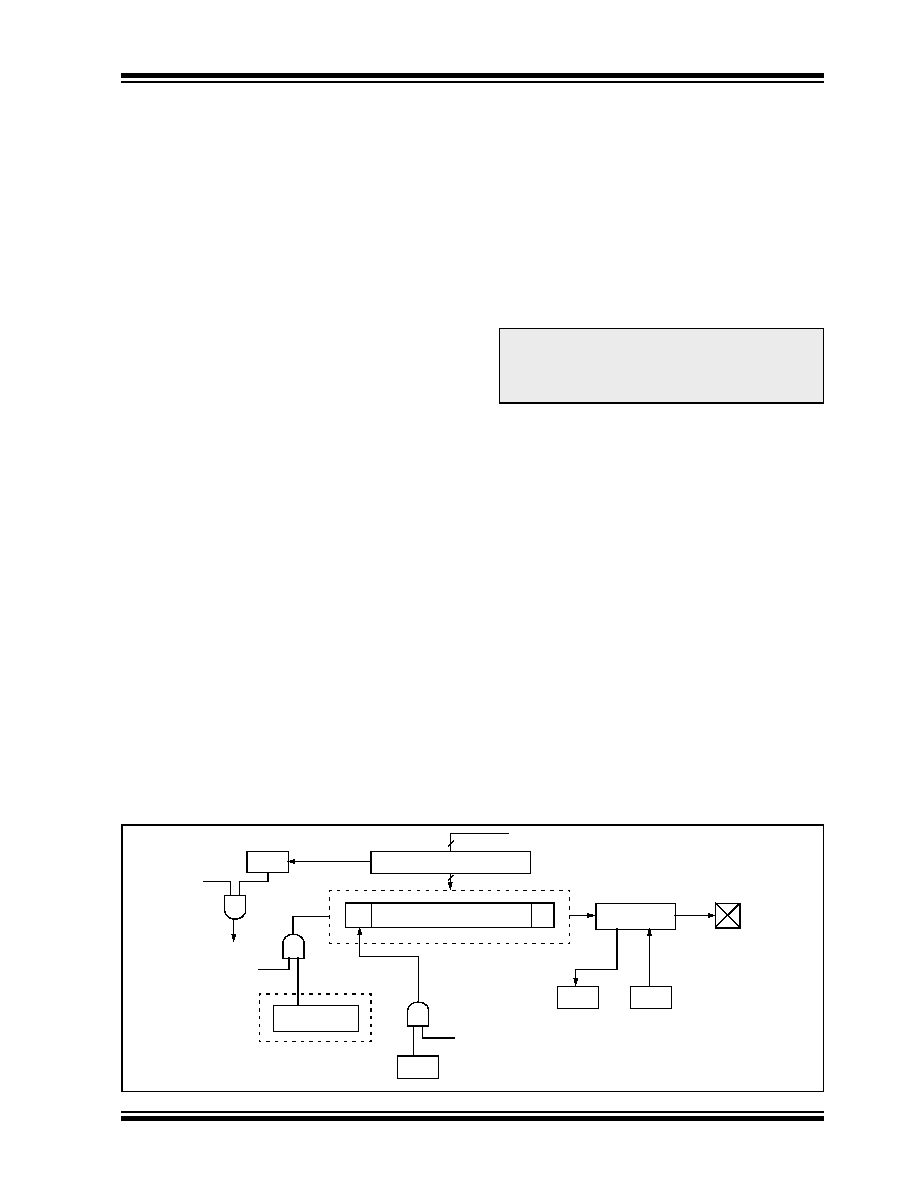

The USART transmitter block diagram is shown in

Figure 10-1. The heart of the transmitter is the transmit

(serial) shift register (TSR). The shift register obtains its

data from the read/write transmit buffer, TXREG. The

TXREG register is loaded with data by firmware. The

TSR register is not loaded until the STOP bit has been

transmitted from the previous load. As soon as the

STOP bit is transmitted, the TSR is loaded with new data

from the TXREG register (if available). Once the TXREG

register transfers the data to the TSR register, the

TXREG register is empty. One instruction cycle later,

flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>)

are set. The TXIF interrupt can be enabled/disabled by

setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF

will be set, regardless of the state of enable bit TXIE and

cannot be cleared in software. It will reset only when new

data is loaded into the TXREG register. While flag bit

TXIF indicates the status of the TXREG register, another

bit TRMT (TXSTA<1>) shows the status of the TSR reg-

ister. Status bit TRMT is a read only bit, which is set one

instruction cycle after the TSR register becomes empty,

and is cleared one instruction cycle after the TSR regis-

ter is loaded. No interrupt logic is tied to this bit, so the

user has to poll this bit in order to determine if the TSR

register is empty.

Transmission is enabled by setting enable bit TXEN

(TXSTA<5>). The actual transmission will not occur until

the TXREG register has been loaded with data and the

baud rate generator (BRG) has produced a shift clock

(Figure 10-2). The transmission can also be started by

first loading the TXREG register and then setting enable

bit TXEN. Normally, when transmission is first started,

the TSR register is empty. At that point, transfer to the

TXREG register will result in an immediate transfer to

TSR, resulting in an empty TXREG. A back-to-back

transfer is thus possible (Figure 10-3). Clearing enable

bit TXEN during a transmission will cause the transmis-

sion to be aborted and will reset the transmitter. As a

result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9

(TXSTA<6>) should be set and the ninth bit should be

written to TX9D (TXSTA<0>). The ninth bit must be writ-

ten before writing the 8-bit data to the TXREG register.

This is because a data write to the TXREG register can

result in an immediate transfer of the data to the TSR

register (if the TSR is empty). In such a case, an incor-

rect ninth data bit may be loaded in the TSR register.

FIGURE 10-1:

USART TRANSMIT BLOCK DIAGRAM

Note 1: The TSR register is not mapped in data

memory, so it is not available to the user.

2: Flag bit TXIF is set when enable bit TXEN

is set. TXIF is cleared by loading TXREG.

TXIF

TXIE

Interrupt

TXEN

Baud Rate CLK

SPBRG

Baud Rate Generator

TX9D

MSb

LSb

Data Bus

TXREG Register

TSR Register

(8)

0

TX9

TRMT

SPEN

RC6/TX/CK pin

Pin Buffer

and Control

8

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8851-16MLL | IC CTLR MAC/PHY NON-PCI 48-LQFP |

| KSZ8873RLL | IC ETHERNET SWITCH 3PORT 64-LQFP |

| KSZ8851-16MQLI | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| KSZ8851-16MQL | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| LTC4278CDKD#PBF | IC PD IEEE 802.3AT 25.5W 32-DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8851-16MLLI TR | 功能描述:以太网 IC 10/100BT Ethernet MAC + PHY with Generic (8, 16-bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLJ | 功能描述:以太网 IC Single-Port Ethernet MAC Controller with 8/16-Bit Non-PCI Interface (125C support) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLJ_10 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:Single-Port Ethernet MAC Controller with 8-Bit or 16-Bit Non-PCI Interface |

| KSZ8851-16MLLU | 功能描述:以太网 IC Single-Port Ethernet Controller (Automotive Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLU TR | 功能描述:以太网 IC Single-Port Ethernet Controller (Automotive Grade) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。