- 您现在的位置:买卖IC网 > PDF目录177663 > LC5256B-10T128I (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5256B-10T128I |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 12 ns, PQFP128 |

| 封装: | TQFP-128 |

| 文件页数: | 64/66页 |

| 文件大小: | 240K |

| 代理商: | LC5256B-10T128I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页当前第64页第65页第66页

Lattice Semiconductor

ispMACH 5000B Family Data Sheet

7

For more information on the sysIO capability, please refer to technical note number TN1000, sysIO Design and

Usage Guidelines available on the Lattice web site at www.latticesemi.com.

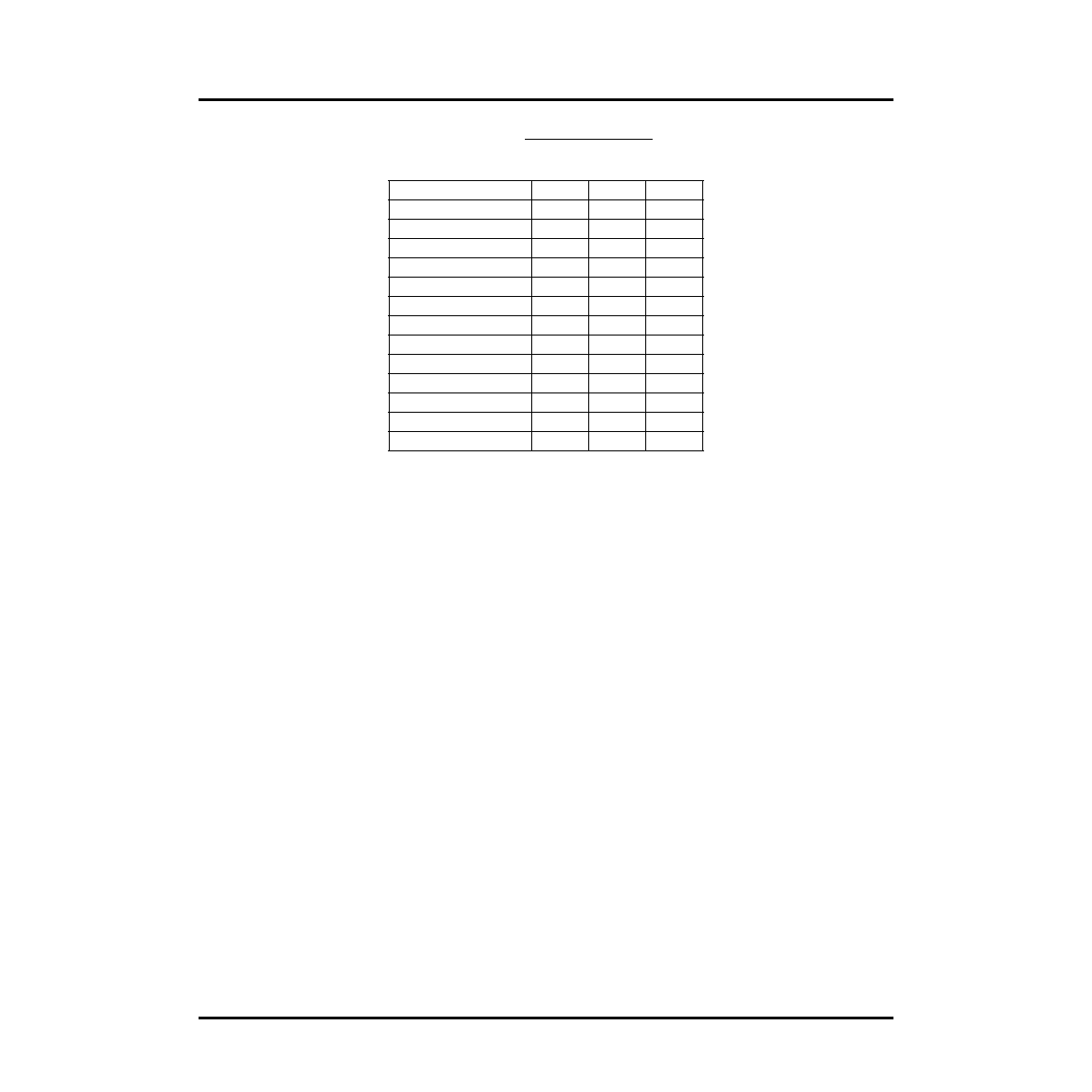

Table 2. ispMACH 5000B Supported I/O Standards

GLB Clock Distribution

The ispLSI 5000B family has four dedicated clock input pins: GCLK0-GCLK3. These feed the Global Clock MUX,

which generates the four global clock signals (CLK0-CLK3). The global clock MUX allows a variety of combinat-

tions of complementary forms of the clock to be used within the device. Additionally, the ispMACH 5000B clock dis-

tribution network offers a differential pair of clock inputs into the global clock MUX for added exibility. Figure 7

shows the global clock MUX.

The global clock pins are arranged in two pairs, GCLK0 and GCLK1 signals are in one pair and GCLK2 and

GCLK3 signals are in the other pair. The pins are arranged on the die such that each pair of external clock signals

can generate one internal clock from either side of the die when used in differential inputs. This arrangement allows

the clock pins to be used either as four single ended clock signals or two differential (LVPECL or LVDS) clock sig-

nal. Both polarities of the clock are available to drive the internal clock distribution networks.

sysIO Standard

VCCO

VREF

VTT

LVTTL

3.3V

N/A

LVCMOS 3.3

3.3V

N/A

LVCMOS 2.5

2.5V

N/A

LVCMOS 1.8

1.8V

N/A

PCI 3.3

3.3V

N/A

AGP-1X

3.3V

N/A

SSTL3, Class I, II

3.3V

1.5V

SSTL2, Class I, II

2.5V

1.25V

CTT 3.3

3.3V

1.5V

CTT 2.5

2.5V

1.25V

HSTL, Class I

1.5V

0.75V

HSTL, Class III

1.5V

0.9

0.75V

GTL+

N/A

1.0V

1.5V

Discontinued

Product

(PCN

#02-06).

Contact

Rochester

Electronics

for

Availability.

www.latticesemi.com/sales/discontinueddevicessales.cfm

相关PDF资料 |

PDF描述 |

|---|---|

| LC5256B-75Q208I | |

| LC5256B-5Q208C | |

| LC5384B-4F256C | |

| LC5256B-4Q208C | |

| LC5384B-5Q208C | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5256B-4F256C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5256B-4Q208C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5256B-4T128C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5256B-5F256C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5256B-5F256I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。