- 您现在的位置:买卖IC网 > PDF目录177666 > LC5512MC-75Q208I (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5512MC-75Q208I |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 9.5 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 13/95页 |

| 文件大小: | 923K |

| 代理商: | LC5512MC-75Q208I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

20

Programmable Slew Rate

The slew rate of outputs is carefully controlled. When outputs are configured as LVCMOS the devices support two

slew rates. This allows system noise and performance to be balanced in a design.

Programmable Bus-Maintenance

All general-purpose inputs have programmable bus maintenance circuitry. These are intended to maintain a valid

logic level into a device when driving devices go into the tri-state mode. Four options are available for users: pull-

up, pull-down, bus-keeper, or nothing.

Expanded In-System Programmability (ispXP)

The ispXPLD 5000MX family utilizes a combination of EEPROM non-volatile cells and SRAM technology to deliver

a logic solution that provides “instant-on” at power-up, a convenient single chip solution, and the capability for infi-

nite reconfiguration. A non-volatile array distributed within the device stores the device configuration. At power-up

this information is transferred in a massively parallel fashion into SRAM bits that control the operation of the device.

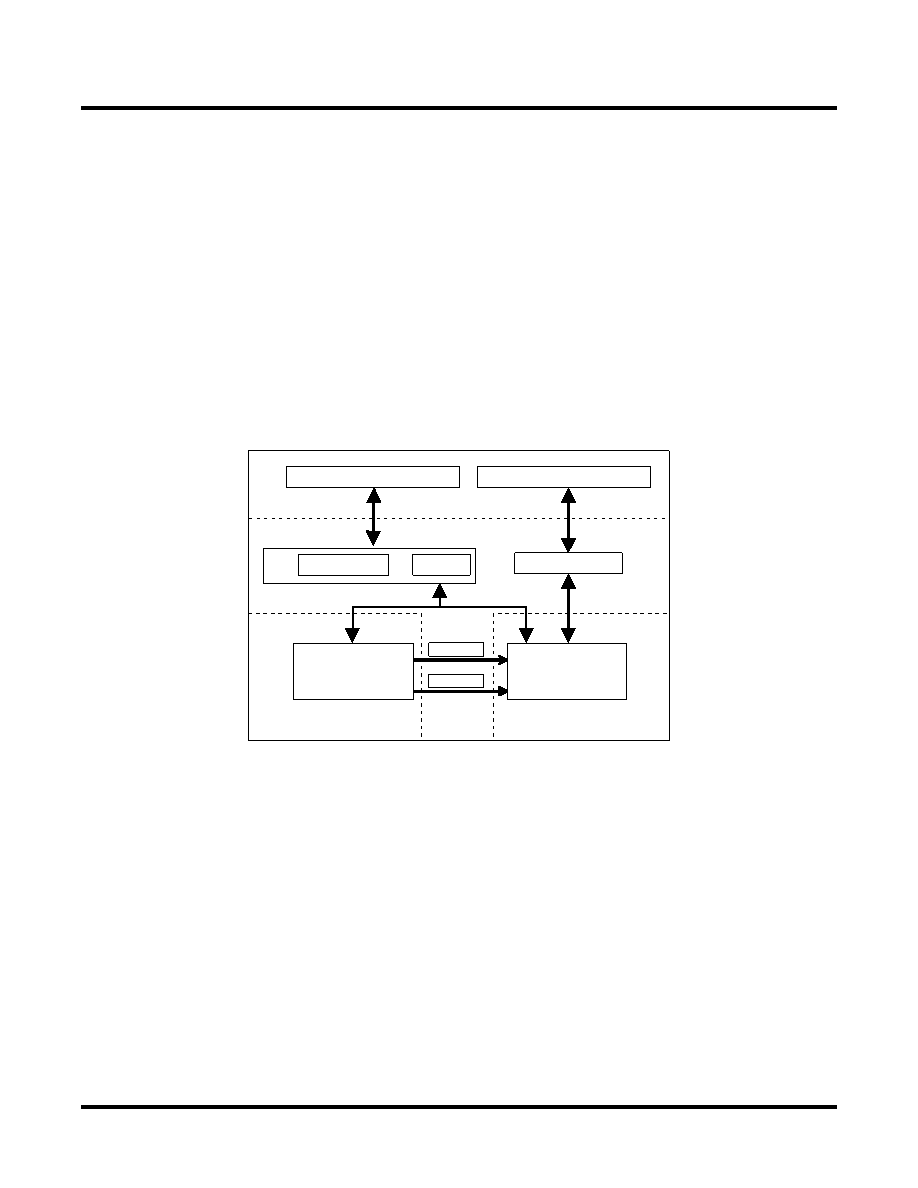

Figure 18 shows the different ports and modes that are used in the configuration and programming of the ispXPLD

5000MX devices.

Figure 18. ispXP Block Diagram

IEEE 1532 ISP

In-system programming of devices provides a number of significant benefits including rapid prototyping, lower

inventory levels, higher quality and the ability to make in-field modifications. All ispXPLD 5000MX devices provide

in-system programmability through their Boundary Scan Test Access Port. This capability has been implemented in

a manner that ensures that the port remains compliant to the IEEE 1532 standard. By using IEEE 1532 as the

communication interface through which ISP is achieved, customers get the benefit of a standard, well-defined inter-

face.

The IEEE1532 programming interface allows programming of either the non-volatile array or reconfiguration of the

SRAM bits.

The ispXPLD 5000MX devices can be programmed across the commercial temperature and voltage range. The

PC-based Lattice software facilitates in-system programming of ispXPLD 5000MX devices. The software takes the

JEDEC file output produced by the design implementation software, along with information about the scan chain,

and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain

via the parallel port of a PC. Alternatively, the software can output files in formats understood by common auto-

mated test equipment. This equipment can then be used to program ispXPLD 5000MX devices during the testing

of a circuit board.

SRAM

Memory Space

E2CMOS

Memory Space

sysCONFIG Peripheral Port

sysCONFIG

ISP 1149.1 TAP Port

Power-up

Refresh

Programming

in seconds

Download in

microseconds

Configuration

in milliseconds

Port

Mode

Memory Space

ISP

1532

BACKGND

相关PDF资料 |

PDF描述 |

|---|---|

| LC5512MC-75F256I | |

| LC5256MC-5F256I | |

| LC5512MB-45F484C | |

| LC5256MC-75F256I | |

| LC51024MC-52F672C | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5512MC-75Q256C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q256I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q484C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q484I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q672C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

发布紧急采购,3分钟左右您将得到回复。