- 您现在的位置:买卖IC网 > PDF目录9218 > LTC6946IUFD-3#PBF (Linear Technology)IC INTEGER-N PLL W/VCO 28-QFN PDF资料下载

参数资料

| 型号: | LTC6946IUFD-3#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 13/30页 |

| 文件大小: | 0K |

| 描述: | IC INTEGER-N PLL W/VCO 28-QFN |

| 软件下载: | PLLWizard™ PLLWizard™, with .NET 2.0 installer |

| 标准包装: | 73 |

| 类型: | 时钟/频率合成器(RF/IF),分数-N,整数-N, |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 5.79GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.15 V ~ 5.25 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-WFQFN 裸露焊盘 |

| 供应商设备封装: | 28-QFN(4x5) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

LTC6946

20

6946fa

OPERATION

STAT Output

The STAT output pin is configured with the x[5:0] bits

of register h01. These bits are used to bit-wise mask, or

enable, the corresponding status flags of status register

h00, according to Equation 2. The result of this bit-wise

Boolean operation is then output on the STAT pin:

STAT = OR (Reg00[5:0] AND Reg01[5:0])

(2)

or expanded:

STAT = (UNLOCK AND x[5]) OR

(ALCHI AND x[4]) OR

(ALCLO AND x[3]) OR

(LOCK AND x[2]) OR

(THI AND x[1]) OR

(TLO AND x[0])

For example, if the application requires STAT to go high

whenever the ALCHI, ALCLO, or THI flags are set, then

x[4], x[3], and x[1] should be set to “1”, giving a register

value of h1A.

Block Power-Down Control

The LTC6946’s power-down control bits are located in

register h02, described in Table 11. Different portions of

the device may be powered down independently. Care must

be taken with the LSB of the register, the POR (power-on

reset) bit. When written to a “1”, this bit forces a full reset of

the part’s digital circuitry to its power-up default state.

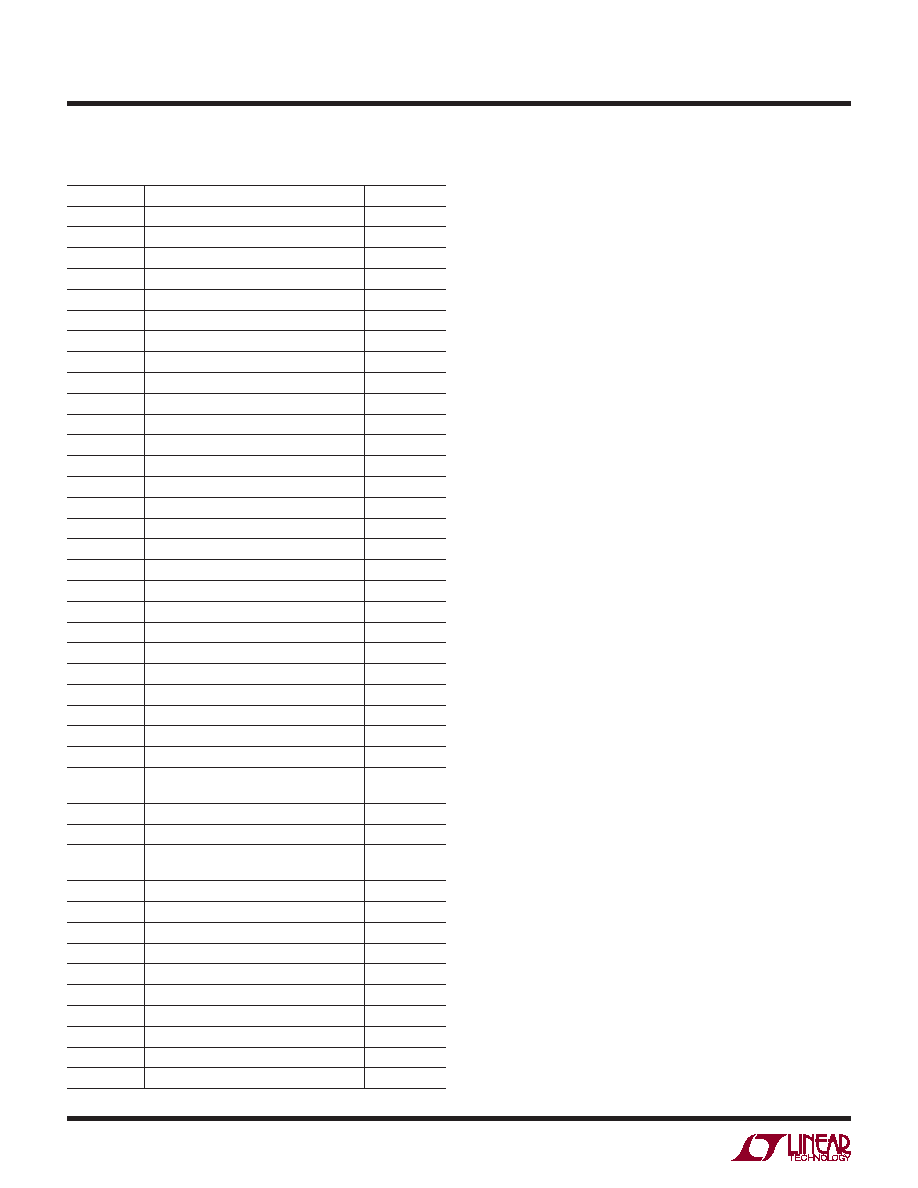

Table 11. Serial Port Register Bit Field Summary

BITS

DESCRIPTION

DEFAULT

ALCCAL

Auto Enable ALC During CAL Operation

1

ALCEN

Always Enable ALC (Override)

1

ALCHI

ALC Too Hi Flag

ALCLO

ALC Too Low Flag

ALCMON

Enable ALC Monitor for Status Flags Only

0

ALCULOK

Enable ALC When PLL Unlocked

0

BD[3:0]

Calibration B Divider Value

h3

BST

REF Buffer Boost Current

1

CAL

Start VCO Calibration (auto clears)

0

CP[3:0]

CP Output Current

hB

CPCHI

CP Enable Hi Voltage Output Clamp

1

CPCLO

CP Enable Low Voltage Output Clamp

1

CPDN

CP Pump Down Only

0

CPINV

CP Invert Phase

0

CPMID

CP Bias to Mid-Rail

1

CPRST

CP Three-State

1

CPUP

CP Pump Up Only

0

CPWIDE

CP Extend Pulse Width

0

FILT[1:0]

REF Input Buffer Filter

h3

LKCT[1:0]

PLL Lock Cycle Count

h1

LKEN

PLL Lock Indicator Enable

1

LKWIN[1:0] PLL Lock Indicator Window

h2

LOCK

PLL Lock Indicator Flag

MTCAL

Mutes Output During Calibration

1

ND[15:0]

N Divider Value (ND[15:0] > 31)

h00FA

OD[2:0]

Output Divider Value (0 < OD[2:0] < 7)

h1

OMUTE

Mutes RF Output

1

PART[4:0]

Part code (h01 for LTC6946-1, h02 for

LTC6946-2, h03 for LTC6946-3 Version)

h01, h02, h03

PDALL

Full Chip Power Down

0

PDOUT

Powers Down O_DIV, RF Output Buffer

0

PDPLL

Powers Down REF, REFO, R_DIV, PFD,

CPUMP, N_DIV

0

PDREFO

Powers Down REFO

1

PDVCO

Powers Down VCO, N_DIV

0

POR

Force Power-On Reset

0

RD[9:0]

R Divider Value (RD[9:0] > 0)

h001

REV[2:0]

Rev Code

h2

RFO[1:0]

RF Output Power

h3

THI

CP Clamp High Flag

TLO

CP Clamp Low Flag

UNLOK

PLL Unlock Flag

x[5:0]

STAT Output OR Mask

h04

相关PDF资料 |

PDF描述 |

|---|---|

| X9429WV14IZ-2.7 | IC XDCP SGL 64-TAP 10K 14-TSSOP |

| LTC6946IUFD-2#PBF | IC INTEGER-N PLL W/VCO 28-QFN |

| VI-B44-IU-B1 | CONVERTER MOD DC/DC 48V 200W |

| SY89429AJZ | IC SYNTHESIZER FREQ PROGR 28PLCC |

| SY58038UMY TR | IC MUX 8:1 PREC 1:2 LVPECL 44MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC6946-x | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 20Msps Low Noise Dual ADC |

| LTC694C | 制造商:LINER 制造商全称:Linear Technology 功能描述:Microprocessor Supervisory Circuits |

| LTC694C-3.3 | 制造商:LINER 制造商全称:Linear Technology 功能描述:3.3V Microprocessor Supervisory Circuits |

| LTC694CN-3.3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Power Supply Supervisor |

| LTC694CN8 | 功能描述:IC MPU SUPERVISORY CIRCUIT 8-DIP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

发布紧急采购,3分钟左右您将得到回复。