- 您现在的位置:买卖IC网 > PDF目录9218 > LTC6946IUFD-3#PBF (Linear Technology)IC INTEGER-N PLL W/VCO 28-QFN PDF资料下载

参数资料

| 型号: | LTC6946IUFD-3#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 7/30页 |

| 文件大小: | 0K |

| 描述: | IC INTEGER-N PLL W/VCO 28-QFN |

| 软件下载: | PLLWizard™ PLLWizard™, with .NET 2.0 installer |

| 标准包装: | 73 |

| 类型: | 时钟/频率合成器(RF/IF),分数-N,整数-N, |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 5.79GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.15 V ~ 5.25 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-WFQFN 裸露焊盘 |

| 供应商设备封装: | 28-QFN(4x5) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

LTC6946

15

6946fa

OPERATION

CHARGE PUMP FUNCTIONS

The charge pump contains additional features to aid

in system start-up and monitoring. See Table 6 for a

summary.

Table 6. Charge Pump Function Bit Descriptions

BIT

DESCRIPTION

CPCHI

Enable High Voltage Output Clamp

CPCLO

Enable Low Voltage Output Clamp

CPDN

Force Sink Current

CPINV

Invert PFD Phase

CPMID

Enable Mid-Voltage Bias

CPRST

Reset PFD

CPUP

Force Source Current

CPWIDE

Extend Current Pulse Width

THI

High Voltage Clamp Flag

TLO

Low Voltage Clamp Flag

The CPCHI and CPCLO bits found in register h0A enable

the high and low voltage clamps, respectively. When CPCHI

is enabled and the CP pin voltage exceeds approximately

VCP+ – 0.9V, the THI status flag is set, and the charge pump

sourcing current is disabled. Alternately, when CPCLO is

enabled and the CP pin voltage is less than approximately

0.9V, the TLO status flag is set, and the charge pump sinking

current is disabled. See Figure 5 for a simplified schematic.

The CPMID bit also found in register h0A enables a resis-

tive VCP+/2 output bias which may be used to pre-bias

troublesome loop filters into a valid voltage range. When

using CPMID, it is recommended to also assert the CPRST

bit, forcing a PFD reset. Both CPMID and CPRST must be

set to “0” for normal operation.

The CPUP and CPDN bits force a constant ICP source or

sink current, respectively, on the CP pin. The CPRST bit

may also be used in conjunction with the CPUP and CPDN

bits, allowing a pre-charge of the loop to a known state,

if required. CPUP, CPDN, and CPRST must be set to “0”

to allow the loop to lock.

The CPWIDE bit extends the charge pump output current

pulse width by increasing the PFD reset path’s delay value

(see Figure 3). CPWIDE is normally set to 0.

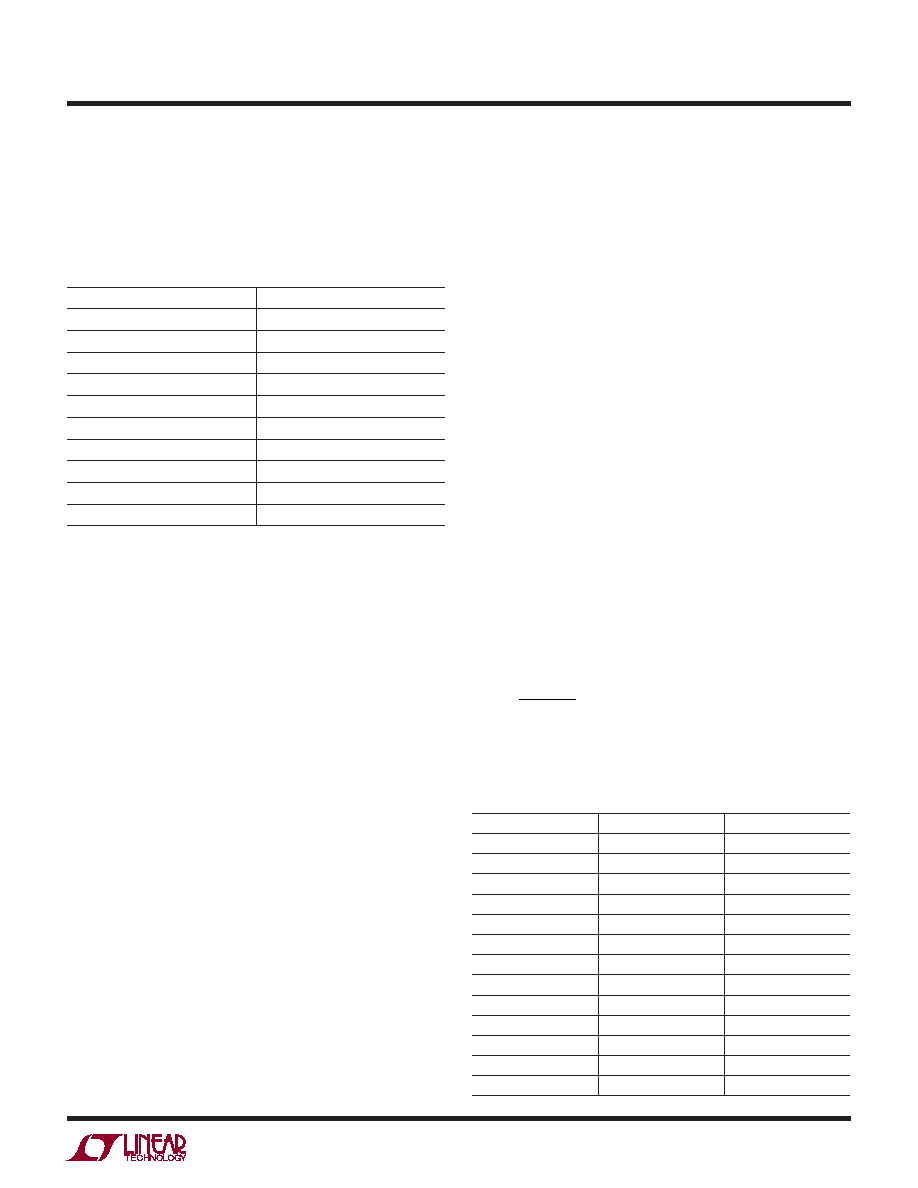

Table 7. BD[3:0] Programming

BD[3:0]

B DIVIDE VALUE

fPFD (MHz)

0

8

<2.4

1

12

2.4 to 3.6

2

16

3.6 to 4.8

3

24

4.8 to 7.2

4

32

7.2 to 9.6

5

48

9.6 to 14

6

64

14 to 19

7

96

19 to 29

8

128

29 to 38

9

192

38 to 58

10

256

58 to 77

11

384

>77

12 to 15

Invalid

VCO

The integrated VCO is available in one of three frequency

ranges. The output frequency range may be further ex-

tended by utilizing the output divider (see Available Options

table, for more details). The wide frequency range of the

VCO, coupled with the output divider capability, allows the

LTC6946 to cover an extremely wide range of continuously

selectable frequencies.

VCO Calibration

The VCO must be calibrated each time its frequency is

changed by either fREF, the R divider, or N divider, but not

the O divider (see the Applications Information section for

the relationship between R, N, O, and the fREF, fPFD, fVCO

and fRF frequencies). The output frequency is then stable

over the LTC6946’s entire temperature range, regardless

of the temperature at which it was calibrated, until the

part is reset due to a power cycle or software power-on

reset (POR).

The output of the B divider is used to clock digital calibra-

tion circuitry as shown in the Block Diagram. The B value,

programmed with bits BD[3:0], is determined according

to Equation 1.

B ≥

fPFD

0.3MHz

(1)

The relationship between bits BD[3:0], the B value, and

fPFD is shown in Table 7.

相关PDF资料 |

PDF描述 |

|---|---|

| X9429WV14IZ-2.7 | IC XDCP SGL 64-TAP 10K 14-TSSOP |

| LTC6946IUFD-2#PBF | IC INTEGER-N PLL W/VCO 28-QFN |

| VI-B44-IU-B1 | CONVERTER MOD DC/DC 48V 200W |

| SY89429AJZ | IC SYNTHESIZER FREQ PROGR 28PLCC |

| SY58038UMY TR | IC MUX 8:1 PREC 1:2 LVPECL 44MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC6946-x | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 20Msps Low Noise Dual ADC |

| LTC694C | 制造商:LINER 制造商全称:Linear Technology 功能描述:Microprocessor Supervisory Circuits |

| LTC694C-3.3 | 制造商:LINER 制造商全称:Linear Technology 功能描述:3.3V Microprocessor Supervisory Circuits |

| LTC694CN-3.3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Power Supply Supervisor |

| LTC694CN8 | 功能描述:IC MPU SUPERVISORY CIRCUIT 8-DIP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 标准包装:1 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:高有效 复位超时:- 电压 - 阀值:1.8V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:6-TSOP(0.059",1.50mm 宽)5 引线 供应商设备封装:5-TSOP 包装:剪切带 (CT) 其它名称:NCP301HSN18T1GOSCT |

发布紧急采购,3分钟左右您将得到回复。