- 您现在的位置:买卖IC网 > PDF目录369885 > LXT384LE Telecomm/Datacomm PDF资料下载

参数资料

| 型号: | LXT384LE |

| 元件分类: | 通信、网络模块及开发工具 |

| 英文描述: | Telecomm/Datacomm |

| 中文描述: | 电信/数据通信 |

| 文件页数: | 30/80页 |

| 文件大小: | 1112K |

| 代理商: | LXT384LE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

LXT384

—

Octal T1/E1/J1 Transceiver

30

Datasheet

2.5

Line Protection

Figure 6 on page 29

shows recommended line interface circuitry. In the receive side, the 1 k

series resistors protect the receiver against current surges coupled into the device. Due to the high

receiver impedance (70 k

typ.) the resistors do not affect the receiver sensitivity. In the transmit

side, the Schottky diodes D1-D4 protect the output driver.While not mandatory for normal

operation, these protection elements are strongly recommended to improve the design robustness.

2.6

Jitter Attenuation

A digital Jitter Attenuation Loop (JAL) combined with a FIFO provides Jitter attenuation. The JAL

is internal and requires no external crystal nor high-frequency (higher than line rate) reference

clock.

In Host Mode, the Global Control Register (GCR) determines whether the JAL is positioned in the

receive or transmit path. In Hardware Mode, the JAL position is determined by the JASEL pin.

The FIFO is a 32 x 2-bit or 64 x 2-bit register (selected by the FIFO64 bit in the GCR). Data is

clocked into the FIFO with the associated clock signal (TCLK or RCLK), and clocked out of the

FIFO with the dejittered JAL clock (

Figure 7

). When the FIFO is within two bits of overflowing or

underflowing, the FIFO adjusts the output clock by

1/8

of a bit period. The Jitter Attenuator

produces a constant delay of 16 or 32 bits in the associated path (refer to test specifications). This

feature can be used for hitless switching applications. This advanced digital jitter attenuator meets

latest jitter attenuation specifications. See

Table 3

.

Under software control, the low limit jitter attenuator corner frequency depends on FIFO length

and the JACF bit setting (this bit is in the GCR register). In Hardware Mode, the FIFO length is

fixed to 64 bits. The corner frequency is fixed to 6 Hz for T1 mode and 3.5 Hz for E1 mode.

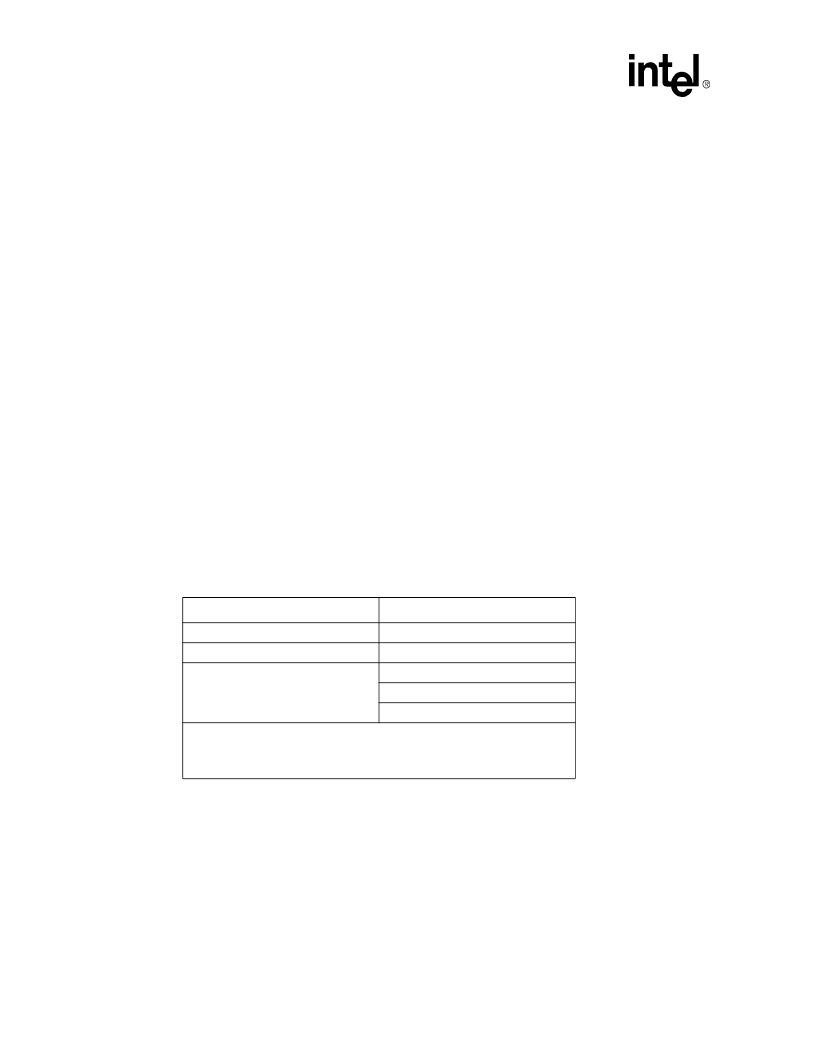

Table 3. Jitter Attenuation Specifications

T1

E1

AT&T Pub 62411

ITU-T G.736

GR-253-CORE

1

ITU-T G.742

3

TR-TSY-000009

2

ITU-T G.783

4

ETSI CTR12/13

BAPT 220

1. Category I, R5-203.

2. Section 4.6.3.

3. Section 6.2 When used with the SXT6234 E2-E1 mux/demux.

4. Section 6.2.3.3 combined jitter when used with the SXT6251 21E1 mapper.

相关PDF资料 |

PDF描述 |

|---|---|

| LXT386BE | PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|BGA|160PIN|PLASTIC |

| LXT386LE | PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| LXT388LE | PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| LXT400JE | Hermetically Sealed, 3.3V, High Speed, High CMR, Logic Gate Optocoupler |

| LXT6155LE | Telecomm/Datacomm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT386 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:QUAD T1/E1/J1 Transceiver |

| LXT386BE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|QUAD|CEPT PCM-30/E-1|CMOS|BGA|160PIN|PLASTIC |

| LXT386LE | 制造商:LEVEL1 功能描述: |

| LXT388LE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| LXT400 | 制造商:LVL1 制造商全称:LVL1 功能描述:All Rate Extended Range Switched 56/DDS Transceiver |

发布紧急采购,3分钟左右您将得到回复。