- 您现在的位置:买卖IC网 > PDF目录69009 > M306N5FCTGP 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | M306N5FCTGP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 0.50 MM PITCH, PLASTIC, LQFP-100 |

| 文件页数: | 25/63页 |

| 文件大小: | 825K |

| 代理商: | M306N5FCTGP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页

Watchdog Timer

Mitsubishi microcomputers

M16C / 62A Group (80-pin)

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

56

Watchdog Timer

The watchdog timer has the function of detecting when the program is out of control. The watchdog timer is

a 15-bit counter which down-counts the clock derived by dividing the BCLK using the prescaler. A watchdog

timer interrupt is generated when an underflow occurs in the watchdog timer. When XIN is selected for the

BCLK

, bit 7 of the watchdog timer control register (address 000F16) selects the prescaler division ratio (by

16 or by 128). When XCIN is selected as the BCLK, the prescaler is set for division by 2 regardless of bit 7

of the watchdog timer control register (address 000F16). Thus the watchdog timer's period can be calcu-

lated as given below. The watchdog timer's period is, however, subject to an error due to the pre-scaler.

BCLK

Write to the watchdog timer

start register

(address 000E16)

RESET

Watchdog timer

interrupt request

Watchdog timer

Set to

“7FFF16”

1/128

1/16

“CM07 = 0”

“WDC7 = 1”

“CM07 = 0”

“WDC7 = 0”

“CM07 = 1”

1/2

Prescaler

For example, suppose that BCLK runs at 16 MHz and that 16 has been chosen for the dividing ratio of the

pre-scaler, then the watchdog timer's period becomes approximately 32.8 ms.

The watchdog timer is initialized by writing to the watchdog timer start register (address 000E16) and when

a watchdog timer interrupt request is generated. The prescaler is initialized only when the microcomputer is

reset. After a reset is cancelled, the watchdog timer and prescaler are both stopped. The count is started by

writing to the watchdog timer start register (address 000E16).

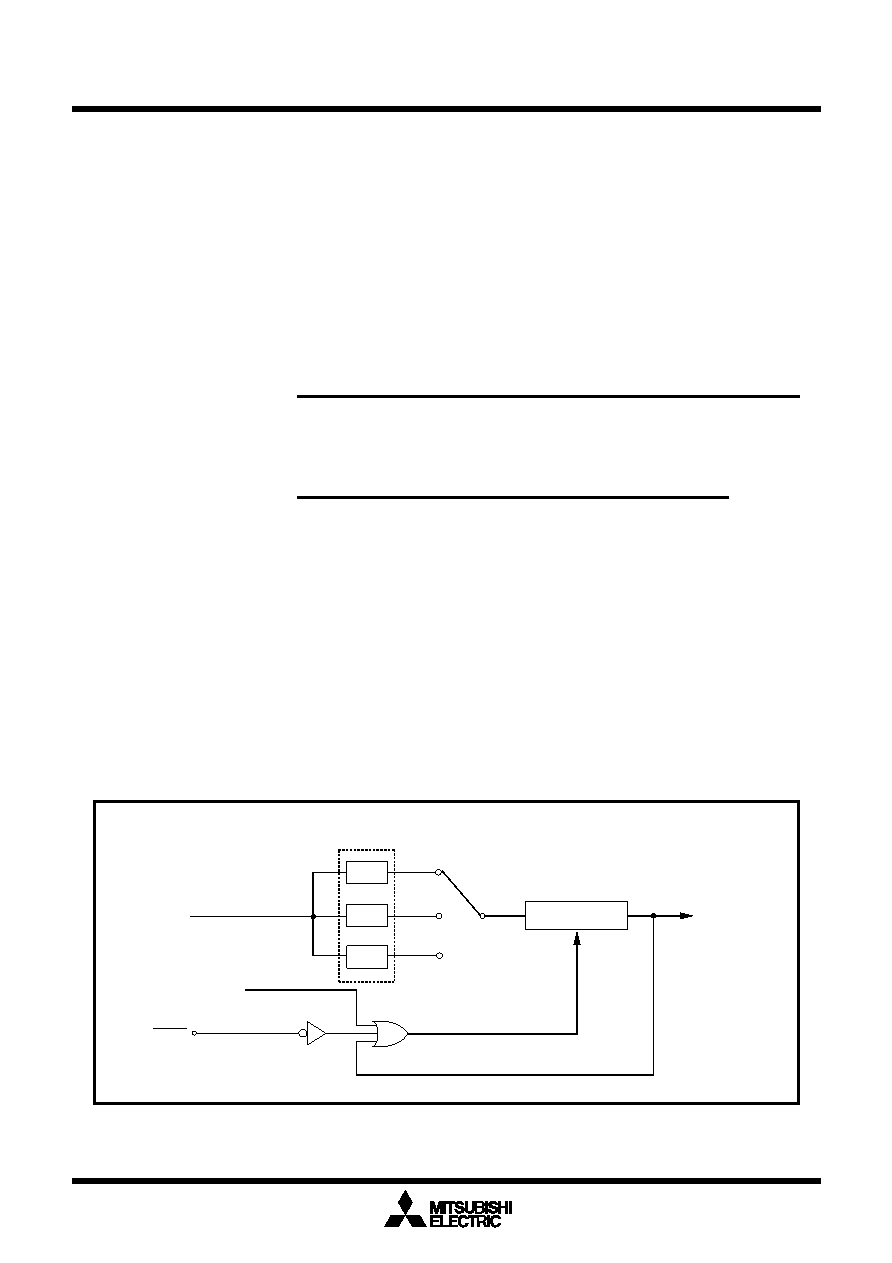

Figure 1.11.1 shows the block diagram of the watchdog timer. Figure 1.11.2 shows the watchdog timer-

related registers.

With XIN chosen for BCLK

Watchdog timer period =

pre-scaler dividing ratio (16 or 128) X watchdog timer count (32768)

BCLK

Figure 1.11.1. Block diagram of watchdog timer

With XCIN chosen for BCLK

Watchdog timer period =

pre-scaler dividing ratio (2) X watchdog timer count (32768)

BCLK

相关PDF资料 |

PDF描述 |

|---|---|

| M306N5FCFP | 16-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCVFP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCVGP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5MCT-XXXGP | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306V0ME-XXXFP | 16-BIT, MROM, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M306N5FCVFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5FCVGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCT-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCT-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCV-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

发布紧急采购,3分钟左右您将得到回复。