- 您现在的位置:买卖IC网 > PDF目录69009 > M306N5FCTGP 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | M306N5FCTGP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 0.50 MM PITCH, PLASTIC, LQFP-100 |

| 文件页数: | 27/63页 |

| 文件大小: | 825K |

| 代理商: | M306N5FCTGP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页

DMAC

Mitsubishi microcomputers

M16C / 62A Group (80-pin)

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

58

DMAC

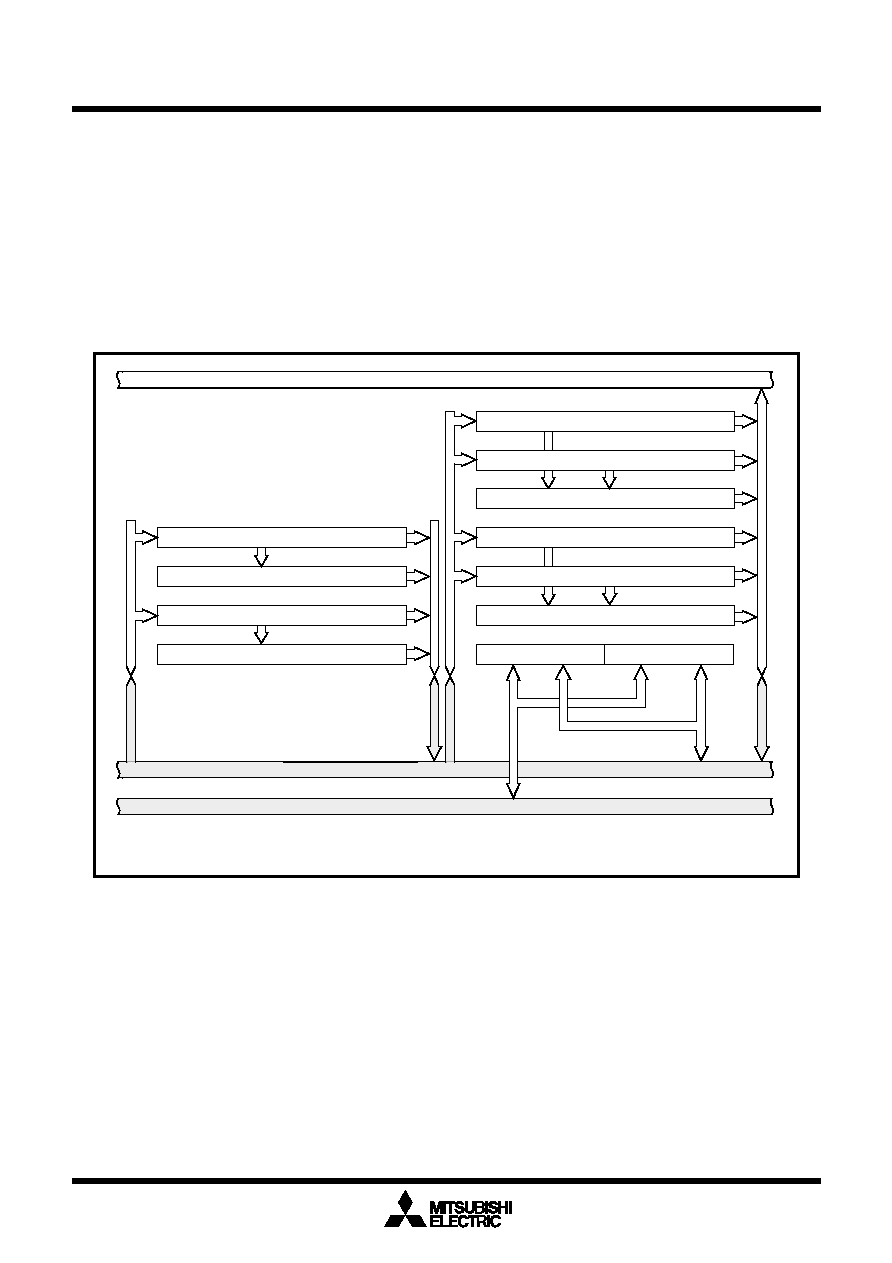

This microcomputer has two DMAC (direct memory access controller) channels that allow data to be sent to

memory without using the CPU. DMAC shares the same data bus with the CPU. The DMAC is given a

higher right of using the bus than the CPU, which leads to working the cycle stealing method. On this

account, the operation from the occurrence of DMA transfer request signal to the completion of 1-word (16-

bit) or 1-byte (8-bit) data transfer can be performed at high speed. Figure 1.12.1 shows the block diagram

of the DMAC. Table 1.12.1 shows the DMAC specifications. Figures 1.12.2 to 1.12.4 show the registers

used by the DMAC.

Figure 1.12.1. Block diagram of DMAC

Data bus low-order bits

DMA latch high-order bits

DMA latch low-order bits

DMA0 source pointer SAR0(20)

DMA0 destination pointer DAR0 (20)

DMA0 forward address pointer (20) (Note)

Data bus high-order bits

Address bus

DMA1 destination pointer DAR1 (20)

DMA1 source pointer SAR1 (20)

DMA1 forward address pointer (20) (Note)

DMA0 transfer counter reload register TCR0 (16)

DMA0 transfer counter TCR0 (16)

DMA1 transfer counter reload register TCR1 (16)

DMA1 transfer counter TCR1 (16)

(addresses 002916, 002816)

(addresses 003916, 003816)

(addresses 002216 to 002016)

(addresses 002616 to 002416)

(addresses 003216 to 003016)

(addresses 003616 to 003416)

Note: Pointer is incremented by a DMA request.

Either a write signal to the software DMA request bit or an interrupt request signal is used as a DMA transfer

request signal. But the DMA transfer is affected neither by the interrupt enable flag (I flag) nor by the

interrupt priority level. The DMA transfer doesn't affect any interrupts either.

If the DMAC is active (the DMA enable bit is set to 1), data transfer starts every time a DMA transfer request

signal occurs. If the cycle of the occurrences of DMA transfer request signals is higher than the DMA

transfer cycle, there can be instances in which the number of transfer requests doesn't agree with the

number of transfers. For details, see the description of the DMA request bit.

相关PDF资料 |

PDF描述 |

|---|---|

| M306N5FCFP | 16-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCVFP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5FCVGP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306N5MCT-XXXGP | 16-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP100 |

| M306V0ME-XXXFP | 16-BIT, MROM, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M306N5FCVFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5FCVGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCT-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCT-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

| M306N5MCV-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:Renesas MCU |

发布紧急采购,3分钟左右您将得到回复。