- 您现在的位置:买卖IC网 > PDF目录67761 > M32000D4BFP-80 32-BIT, 80 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | M32000D4BFP-80 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 80 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | 14 X 20 MM, 0.65 MM PITCH, PLASTIC, LQFP-100 |

| 文件页数: | 9/44页 |

| 文件大小: | 448K |

| 代理商: | M32000D4BFP-80 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

M32000D4BFP-80

17

Internal memory system

The memory system built into the M32000D4BFP-80 has the follow-

ing characteristics.

internal 16M-bit (2M-byte) DRAM

internal 4K-byte cache memory

CPU, cache and internal DRAM are connected by a 128-bit bus

selectable cache memory operation mode

– internal instruction/data cache mode

– instruction cache mode

– cache-off mode

When the internal instruction/data cache mode is selected, the cache

memory functions as a cache for both instruction and data from the

internal DRAM, and caches all bus access to the DRAM. This mode

is for a system which uses the internal DRAM as main memory. Trans-

fer between the M32R CPU, cache memory and internal DRAM is

always carried out in blocks of 128 bits. Caching is carried out by the

direct map method. Writing is by the copy back method.

When the M32000D4BFP-80 access destination is an external space,

data transfer between the M32R CPU and the external device is car-

ried out via the bus interface unit (BIU). The BIU has a 128-bit data

buffer which converts the bus width between the 128-bit bus in the

M32000D4BFP-80 and the external bus. Caching is not applicable in

this case of data transfer.

When accessing the internal DRAM from an external bus master,

and a cache hit occurs (the accessed data is inside the cache), data

transfer between the cache memory and the external bus via the BIU

is carried out. When a cache miss occurs, (the accessed data is not

inside the cache) data transfer is carried out between the internal

DRAM and the external bus via the BIU without cache replacement.

cache control register (MCCR) < address: H'FFFF FFFF>

D24

D25

D26

D27

D28

D29

D30

D31

CP

CM0

CM1

<at reset: H'01>

D

bit name

function

R

W

24

CP

0: no purge

0

(cache purge)

1: purge

25 - 29

Not assigned.

0

!

30, 31

CM0, CM1

00: cache mode

(cache mode)

is not changed

01: cache-off mode

10: internal

instruction/data

cache mode

11: instruction cache

mode

R = 0 ... "0" when reading

R =

... read enabled

W =

... write enabled

W =

: write disabled

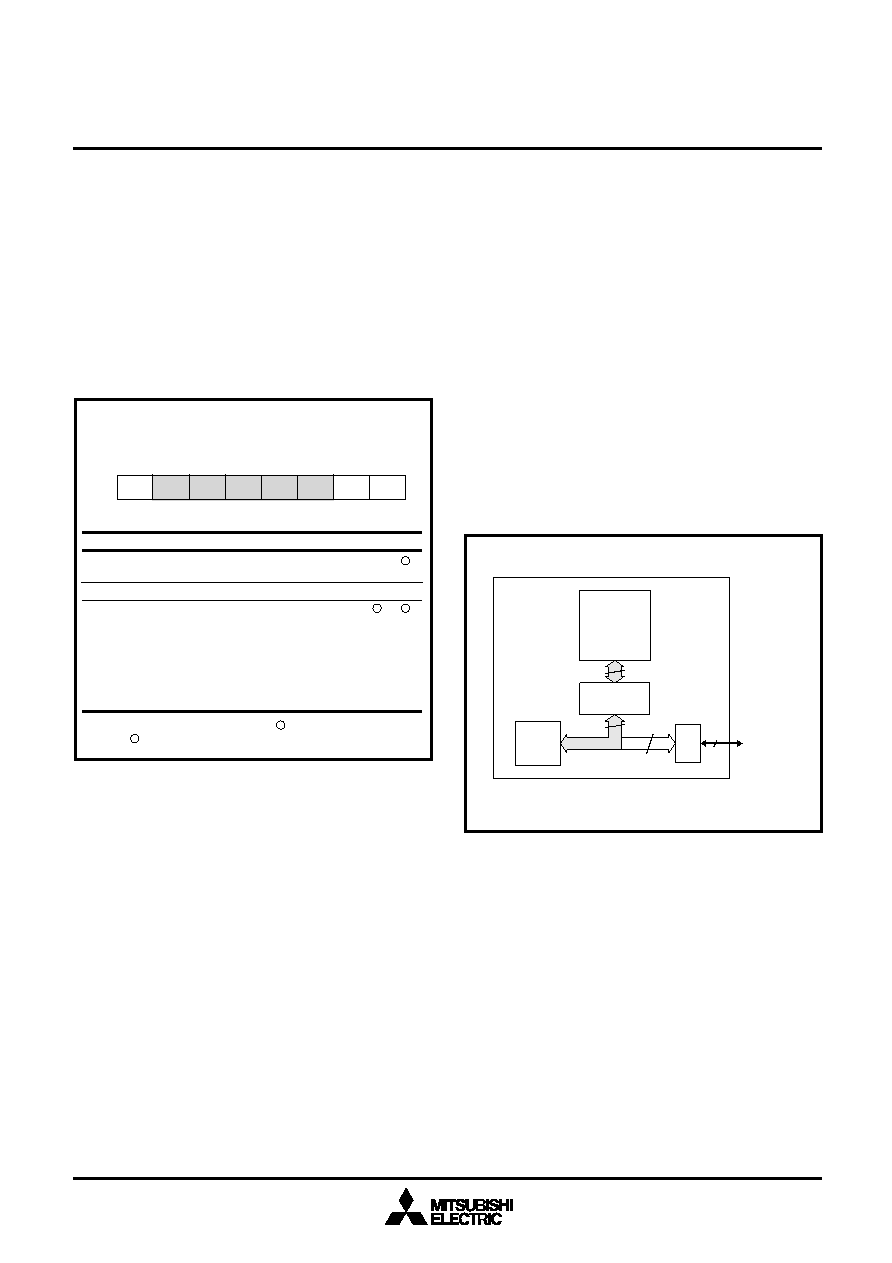

Fig. 12 Cache control register

Fig. 13 Internal instruction/data cache mode

128

external bus

(16 bits)

16

external bus

interface

M32000D4BFP-80

128

instruction/

data cache

DRAM

BIU

CPU

!

相关PDF资料 |

PDF描述 |

|---|---|

| M32171F4VFP | 32-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

| M32171F3VFP | 32-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

| M32173F2VFP | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP144 |

| M32172F2VFP | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP144 |

| M32186F8VFP | 32-BIT, FLASH, 80 MHz, RISC MICROCONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M32002AGLJ | 制造商:MTRONPTI 制造商全称:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AGMJ | 制造商:MTRONPTI 制造商全称:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AGPJ | 制造商:MTRONPTI 制造商全称:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AMLJ | 制造商:MTRONPTI 制造商全称:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AMMJ | 制造商:MTRONPTI 制造商全称:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

发布紧急采购,3分钟左右您将得到回复。