- 您现在的位置:买卖IC网 > PDF目录69010 > M34238MK-XXXGP 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | M34238MK-XXXGP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | PLASTIC, SOP-20 |

| 文件页数: | 2/41页 |

| 文件大小: | 243K |

| 代理商: | M34238MK-XXXGP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

MITSUBISHI MICROCOMPUTERS

4238 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER for INFRARED REMOTE CONTROL TRANSMITTERS

9

CARR PORT OUTPUT MONITOR TIMER

When the system clock starts oscillating as the system is returned

from a standby state by inputting a rising waveform (from low to high)

________________

to RESET pin, or by pulling the key-on wakeup input pin low, the

CARR port output monitor timer starts up. Then, when the CARR port

output monitor timer reaches 8192 counts of system clock, the pro-

gram counter starts operating. If the port CARR output latch is set to

“1” before the CARR port output monitor timer reaches 72704 counts

of system clock pulses (when instruction clock = f(XIN)/4 selected) af-

ter it starts operating, the CARR port output monitor timer is cleared

to “0” and starts over again beginning with “0”. (Each time the port

CARR output latch is set to “1” with the OCRA instruction, the CARR

port output monitor timer is cleared to “0”.) If the port CARR output

latch is not set to “1” until the CARR port output monitor timer

reaches 72704 counts of system clock, the system enters a standby

state.

Note that the CARR port output monitor timer can neither be read nor

written by software.

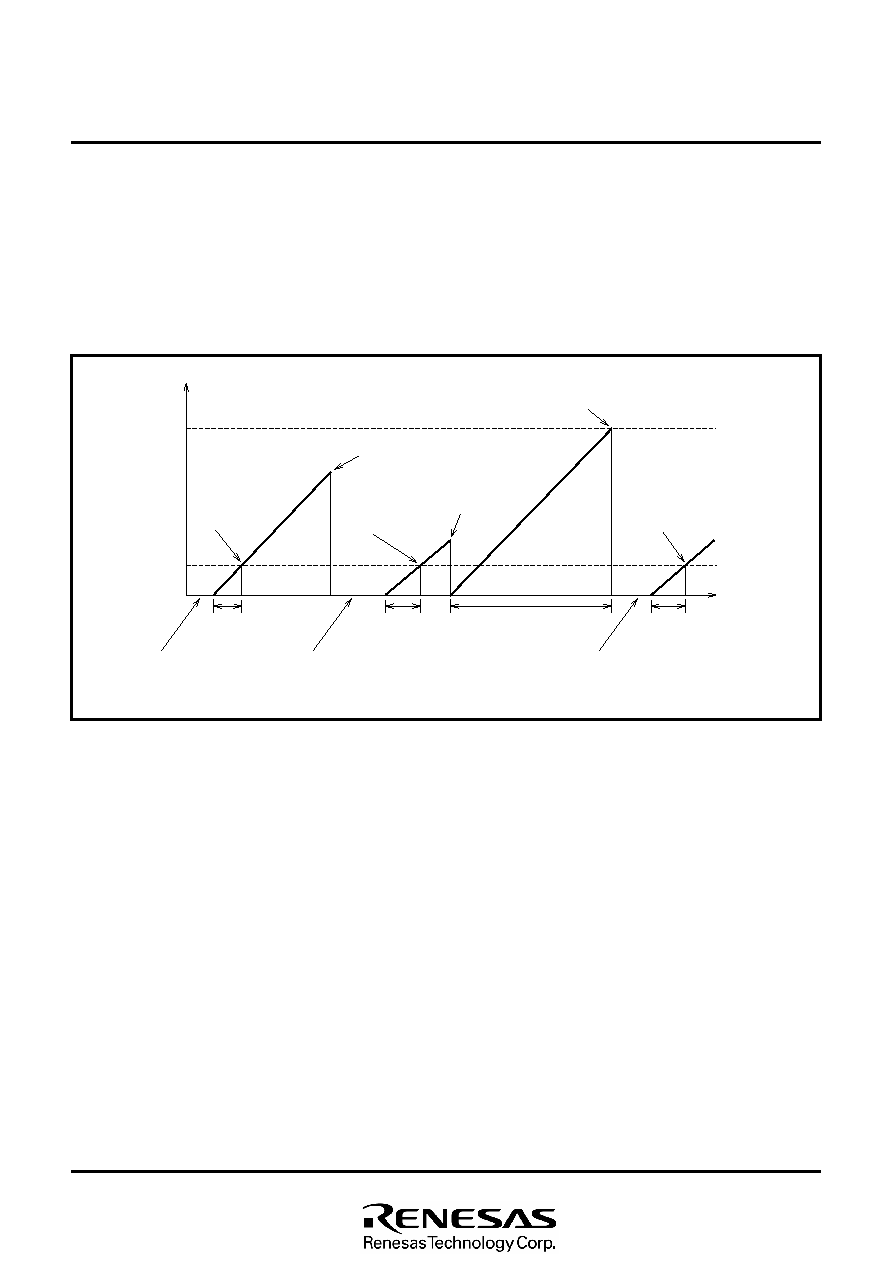

Figure 13 shows operation of the CARR port output monitor timer.

Fig. 13 CARR port output monitor timer operation

STANDBY STATE

When the CARR port output monitor timer overflows, the system en-

ters a standby state. In a standby state, the contents of RAM, regis-

ters, and ports are not retained. The oscillator circuit stops operating

and the CPU is placed in its initial state.

The system is returned from a standby state by inputting a rising

____________

waveform (from low to high) to RESET pin, or by pulling the key-on

wakeup input pin low, starting up the program from address 0 in page

0.

RAM BACK-UP STATE

The system enters a RAM back-up state by executing the POF in-

struction. In a RAM back-up state, the contents of RAM is retained,

but the contents of registers and ports are not retained. The oscilla-

tion circuit stops operating and the CPU is placed in its initial state.

The system is returned from a RAM back-up state by pulling the key-

on wakeup input pin low, starting up the program from address 0 in

page 0.

The M34238MK-XXXGP has a flag P to determine whether or not to

return from a RAM back-up state. The flag P is set to “1” only when

the system is returned from a RAM back-up state; it is cleared to “0”

when the system starts up a program after a reset or is returned from

a standby state.

The state of flag P can be examined with the SNZP instruction.

Count value

Program

counter

starts

Program

counter

starts

Program

counter

starts

OCRA instruction

is executed

POF instruction is executed

CARR port output

monitor timer overflows

18ms

(2.25ms)

0

18ms

(2.25ms)

18ms

(2.25ms)

159.8ms

(144ms)

Reset state

RAM back-up state

Standby state

Time

Note : Indicated above are the time and count value when f(XIN) = 455kHz and instruction clock = f(XIN)/4 are selected.

Enclosed in parentheses are the time and count value when f(XIN) = 3.64 MHz and instruction clock = f(XIN)/32 are selected.

72704

(524288)

8192

(8192)

相关PDF资料 |

PDF描述 |

|---|---|

| M34250E2-XXXFP | 4-BIT, OTPROM, 4.4 MHz, MICROCONTROLLER, PDSO20 |

| M34250M2-XXXFP | 4-BIT, MROM, 4.4 MHz, MICROCONTROLLER, PDSO20 |

| M34250M2-XXXFP | 4-BIT, MROM, 4.4 MHz, MICROCONTROLLER, PDSO20 |

| M34280M1-XXXFP | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M34280M1-XXXGP | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M3424 SL001 | 制造商:Alpha Wire Company 功能描述:CBL 6PR 24AWG SLT 1000' |

| M3424 SL002 | 制造商:Alpha Wire Company 功能描述:CBL 6PR 24AWG SLT 500' |

| M3424 SL005 | 制造商:Alpha Wire Company 功能描述:CBL 6PR 24AWG SLT 100' |

| M3424-0003 | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING TRANSISTOR |

| M3424-SL002 | 制造商:Alpha Wire 功能描述: |

发布紧急采购,3分钟左右您将得到回复。