- 您现在的位置:买卖IC网 > PDF目录80428 > M37540M2T-XXXFP 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 PDF资料下载

参数资料

| 型号: | M37540M2T-XXXFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| 封装: | 7 X 7 MM, 0.80 MM PITCH, PLASTIC, LQFP-32 |

| 文件页数: | 40/88页 |

| 文件大小: | 872K |

| 代理商: | M37540M2T-XXXFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

7540 Group

Rev.4.00

Jun 21, 2004

page 45 of 82

REJ03B0011-0400Z

q Oscillation stop detection circuit (Note)

The oscillation stop detection circuit is used for reset occurrence

when a ceramic resonator or an oscillation circuit stops by discon-

nection. When internal reset occurs, reset because of oscillation

stop can be detected by setting “1” to the oscillation stop detection

status bit.

Also, when using the oscillation stop detection circuit, an on-chip

oscillator is required.

Figure 53 shows the state transition.

Note: The oscillation stop detection circuit is not included in the

emulator MCU “M37540RSS”.

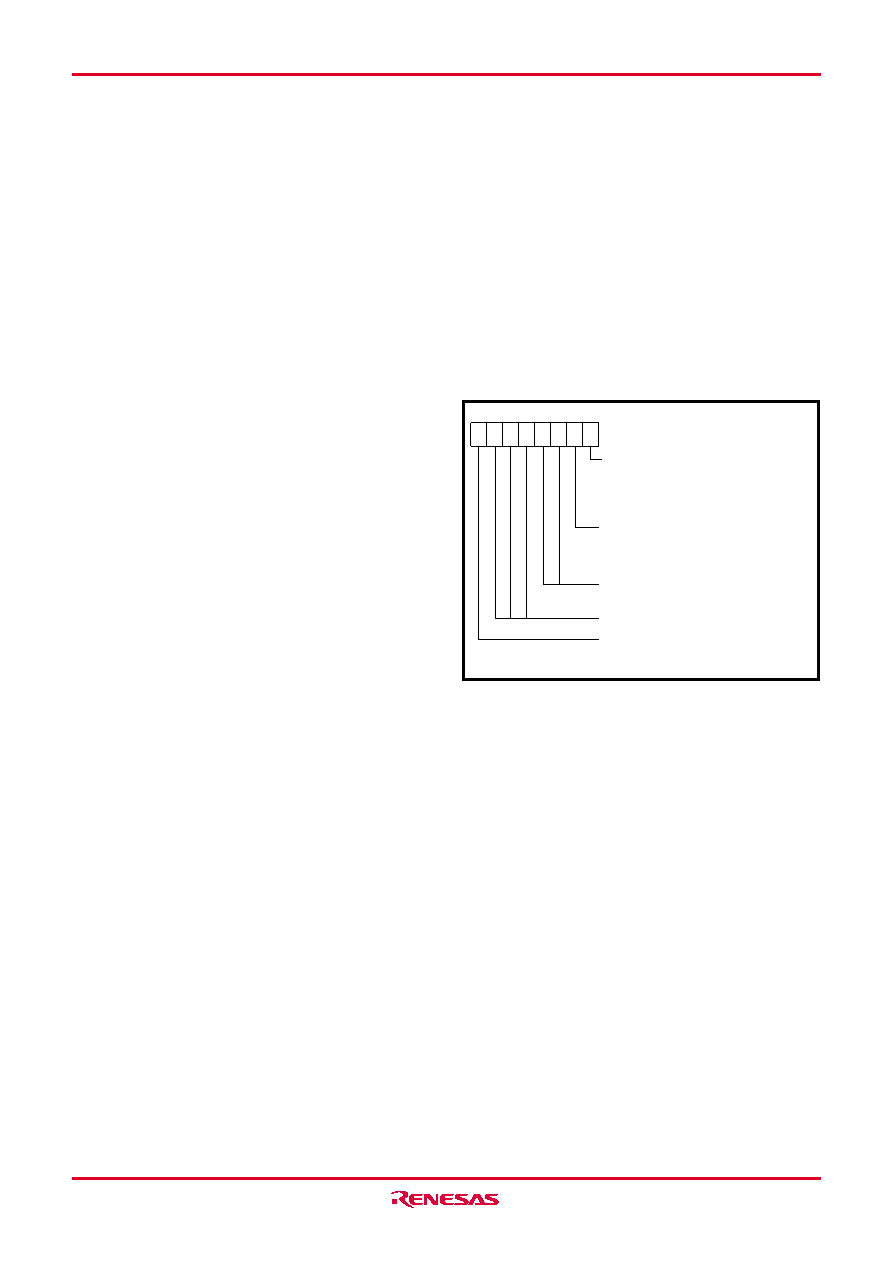

Fig. 50 Structure of MISRG

MISRG(address 003816, initial value: 0016)

b7

b0

Oscillation stabilization time set bit after

release of the STP instruction

0: Set “0116” in timer1, and “FF16”

in prescaler 1 automatically

1: Not set automatically

Ceramic or RC oscillation stop detection

function active bit

0: Detection function inactive

1: Detection function active

Reserved bits (return “0” when read)

(Do not write “1” to these bits)

Not used (return “0” when read)

Oscillation stop detection status bit

0: Oscillation stop not detected

1: Oscillation stop detected

(1) Oscillation control

Stop mode

When the STP instruction is executed, the internal clock

φ stops at

an “H” level and the XIN oscillator stops. At this time, timer 1 is set

to “0116” and prescaler 1 is set to “FF16” when the oscillation sta-

bilization time set bit after release of the STP instruction is “0”. On

the other hand, timer 1 and prescaler 1 are not set when the

above bit is “1”. Accordingly, set the wait time fit for the oscillation

stabilization time of the oscillator to be used. f(XIN)/16 is forcibly

connected to the input of prescaler 1. When an external interrupt

is accepted, oscillation is restarted but the internal clock

φ remains

at “H” until timer 1 underflows. As soon as timer 1 underflows, the

internal clock

φ is supplied. This is because when a ceramic oscil-

lator is used, some time is required until a start of oscillation. In

case oscillation is restarted by reset, no wait time is generated. So

apply an “L” level to the RESET pin while oscillation becomes

stable.

Also, the STP instruction cannot be used while CPU is operating

by an on-chip oscillator.

Wait mode

If the WIT instruction is executed, the internal clock

φ stops at an

“H” level, but the oscillator does not stop. The internal clock re-

starts if a reset occurs or when an interrupt is received. Since the

oscillator does not stop, normal operation can be started immedi-

ately after the clock is restarted. To ensure that interrupts will be

received to release the STP or WIT state, interrupt enable bits

must be set to “1” before the STP or WIT instruction is executed.

s Notes on clock generating circuit

For use with the oscillation stabilization set bit after release of the

STP instruction set to “1”, set values in timer 1 and prescaler 1 af-

ter fully appreciating the oscillation stabilization time of the

oscillator to be used.

Switch of ceramic and RC oscillations

After releasing reset the operation starts by starting an on-chip os-

cillator. Then, a ceramic oscillation or an RC oscillation is selected

by setting bit 5 of the CPU mode register.

Double-speed mode

When a ceramic oscillation is selected, a double-speed mode can

be used. Do not use it when an RC oscillation is selected.

CPU mode register

Bits 5, 1 and 0 of CPU mode register are used to select oscillation

mode and to control operation modes of the microcomputer. In or-

der to prevent the dead-lock by error-writing (ex. program

run-away), these bits can be rewritten only once after releasing re-

set. After rewriting it is disable to write any data to the bit. (The

emulator MCU “M37540RSS” is excluded.)

Also, when the read-modify-write instructions (SEB, CLB) are ex-

ecuted to bits 2 to 4, 6 and 7, bits 5, 1 and 0 are locked.

Clock division ratio, XIN oscillation control, on-chip oscillator control

The state transition shown in Fig. 52 can be performed by setting

the clock division ratio selection bits (bits 7 and 6), XIN oscillation

control bit (bit 4), on-chip oscillator oscillation control bit (bit 3) of

CPU mode register. Be careful of notes on use in Fig. 52.

相关PDF资料 |

PDF描述 |

|---|---|

| M37540M2V-XXXFP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| M37540M4V-XXXGP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO36 |

| M30624MGP-XXXGP | 16-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP100 |

| M37478E8SP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| MC68HC908GR8AMDW | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M37540M2T-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:8-BIT CISC SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 740 SERIES |

| M37540M2V-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37540M2V-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:8-BIT CISC SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 740 SERIES |

| M37540M2-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:8-BIT CISC SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 740 SERIES |

| M37540M2-XXXGP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

发布紧急采购,3分钟左右您将得到回复。