- 您现在的位置:买卖IC网 > PDF目录296386 > M392T5160CJA-CCC 512M X 72 DDR DRAM MODULE, 0.6 ns, DMA240 PDF资料下载

参数资料

| 型号: | M392T5160CJA-CCC |

| 元件分类: | DRAM |

| 英文描述: | 512M X 72 DDR DRAM MODULE, 0.6 ns, DMA240 |

| 封装: | DIMM-240 |

| 文件页数: | 7/30页 |

| 文件大小: | 718K |

| 代理商: | M392T5160CJA-CCC |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

Rev. 1.3 July 2007

RDIMM

DDR2 SDRAM

15 of 30

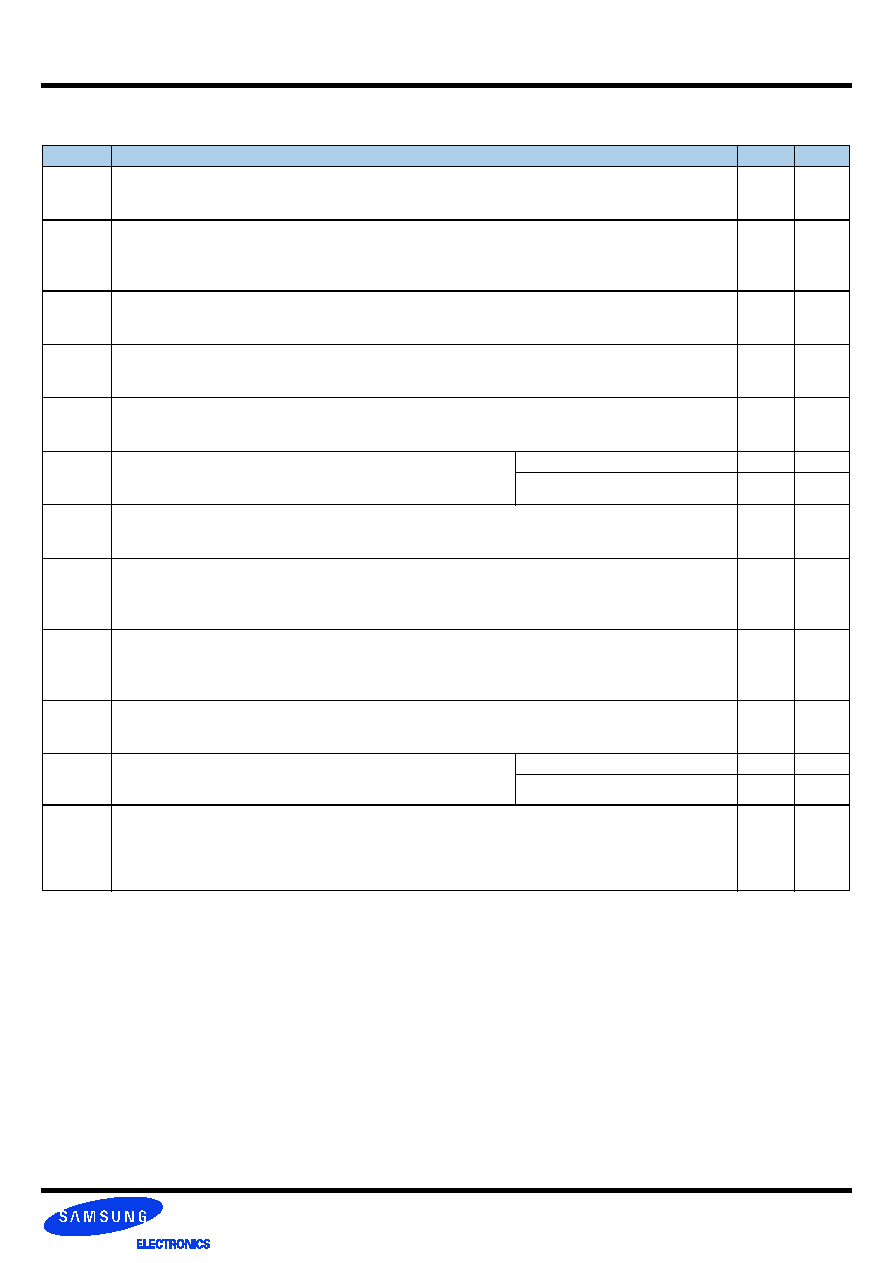

(IDD values are for full operating range of Voltage and Temperature)

Symbol

Proposed Conditions

Units

Note

IDD0

Operating one bank active-precharge current;

tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands;

Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD1

Operating one bank active-read-precharge current;

IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD =

tRCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern

is same as IDD4W

mA

IDD2P

Precharge power-down current;

All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are

FLOATING

mA

IDD2Q

Precharge quiet standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are STABLE; Data

bus inputs are FLOATING

mA

IDD2N

Precharge standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING;

Data bus inputs are SWITCHING

mA

IDD3P

Active power-down current;

All banks open; tCK = tCK(IDD); CKE is LOW; Other control and address

bus inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0mA

mA

Slow PDN Exit MRS(12) = 1mA

mA

IDD3N

Active standby current;

All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD4W

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP

= tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus

inputs are SWITCHING

mA

IDD4R

Operating burst read current;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRAS-

max(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCH-

ING; Data pattern is same as IDD4W

mA

IDD5B

Burst auto refresh current;

tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid commands;

Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD6

Self refresh current;

CK and CK\ at 0V; CKE

≤ 0.2V; Other control and address bus inputs are

FLOATING; Data bus inputs are FLOATING

Normal

mA

Low Power

mA

IDD7

Operating bank interleave read current;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = tRCD(IDD)-1*tCK(IDD); tCK = tCK(IDD), tRC =

tRC(IDD), tRRD = tRRD(IDD), tFAW = tFAW(IDD), tRCD = 1*tCK(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; Refer to the fol-

lowing page for detailed timing conditions

mA

10.0 IDD Specification Parameters Definition

相关PDF资料 |

PDF描述 |

|---|---|

| M3933/14-02N | 0 MHz - 12400 MHz RF/MICROWAVE FIXED ATTENUATOR |

| MIL-A-3933/14-02 | 0 MHz - 12400 MHz RF/MICROWAVE FIXED ATTENUATOR |

| MIL-A-3933/14-14 | 0 MHz - 12400 MHz RF/MICROWAVE FIXED ATTENUATOR |

| M3933/14-18S | 0 MHz - 12400 MHz RF/MICROWAVE FIXED ATTENUATOR |

| MIL-A-3933/14-17 | 0 MHz - 12400 MHz RF/MICROWAVE FIXED ATTENUATOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M392T5160CJA-CF7 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Registered SDRAM MODULE |

| M392T5160QJMA | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

| M392T5660FBA | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

| M392T5660QZHA | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

| M392T5663FBA | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

发布紧急采购,3分钟左右您将得到回复。