- 您现在的位置:买卖IC网 > PDF目录9827 > MAX1124EGK+TD (Maxim Integrated Products)IC ADC 10BIT PAR 250MSPS 68QFN PDF资料下载

参数资料

| 型号: | MAX1124EGK+TD |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 2/17页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT PAR 250MSPS 68QFN |

| 标准包装: | 2,500 |

| 位数: | 10 |

| 采样率(每秒): | 250M |

| 数据接口: | LVDS,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 657mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | * |

| 封装/外壳: | * |

| 供应商设备封装: | * |

| 包装: | * |

| 输入数目和类型: | 1 个单端,单极;1 个差分,单极 |

MAX1124

Detailed Description—Theory

of Operation

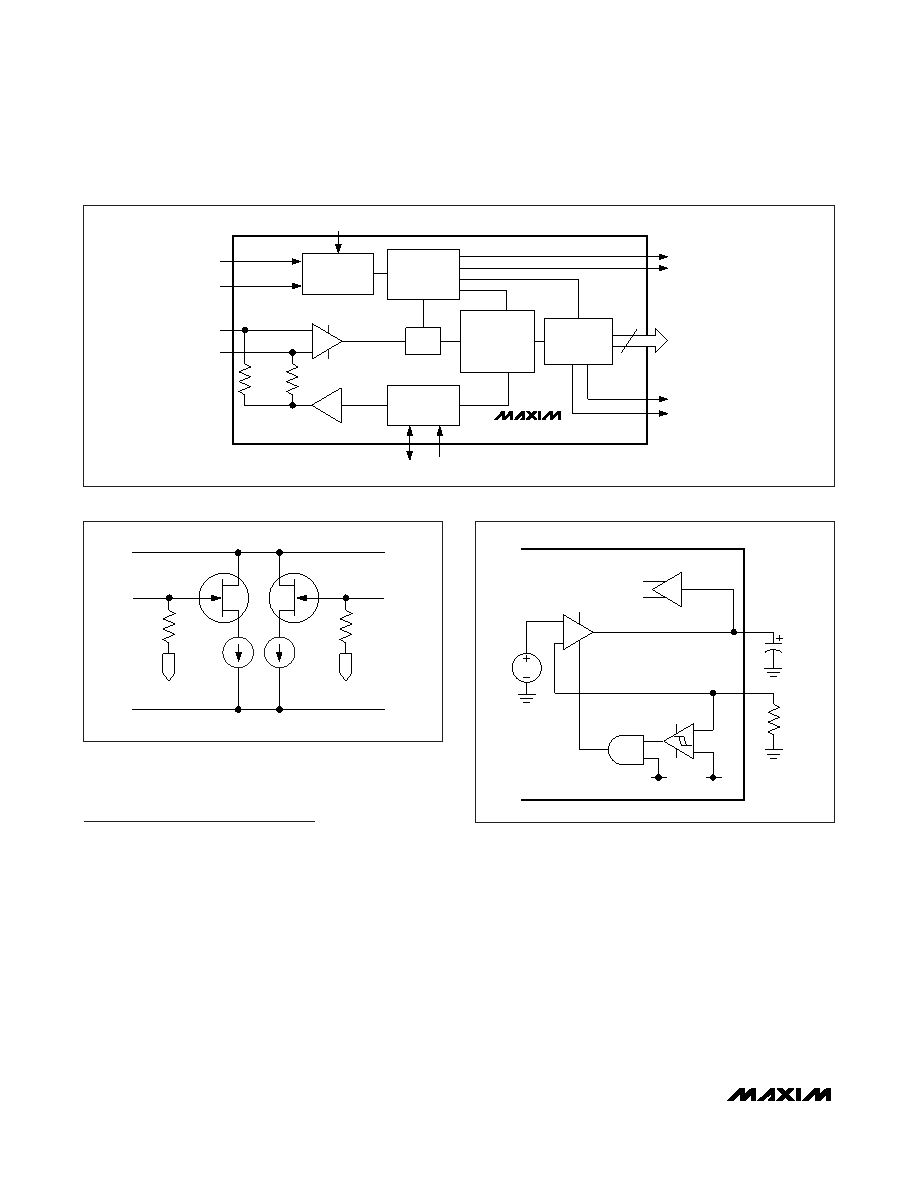

The MAX1124 uses a fully differential, pipelined archi-

tecture that allows for high-speed conversion, opti-

mized accuracy and linearity, while minimizing power

consumption and die size.

Both positive (INP) and negative/complementary analog

input terminals (INN) are centered around a common-

mode voltage of 1.4V, and accept a differential analog

input voltage swing of ±0.3125V each, resulting in a typi-

cal differential full-scale signal swing of 1.25VP-P.

INP and INN are buffered prior to entering each track-

and-hold (T/H) stage and are sampled when the differen-

tial sampling clock signal transitions high. A 2-bit ADC

following the first T/H stage then digitizes the signal, and

controls a 2-bit digital-to-analog converter (DAC).

Digitized and reference signals are then subtracted,

resulting in a fractional residue signal that is amplified

before it is passed on to the next stage through another

T/H amplifier. This process is repeated until the applied

input signal has successfully passed through all stages

of the 10-bit quantizer. Finally, the digital outputs of all

stages are combined and corrected for in the digital cor-

rection logic to generate the final output code. The result

is a 10-bit parallel digital output word in user-selectable

two’s complement or binary output formats with LVDS-

compatible output levels. See Figure 1 for a more

detailed view of the MAX1124 architecture.

1.8V, 10-Bit, 250Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

10

______________________________________________________________________________________

CLOCK-

DIVIDER

CONTROL

CLOCK

MANAGEMENT

T/H

10-BIT PIPELINE

QUANTIZER CORE

REFERENCE

LVDS

DATA PORT

10

COMMON-MODE

BUFFER

INPUT

BUFFER

CLKDIV

CLKP

CLKN

INP

INN

REFIO REFADJ

2.2k

Ω

2.2k

Ω

DCLKP

DCLKN

D0P/N–D9P/N

ORP

ORN

MAX1124

Figure 1. MAX1124 Block Diagram

AVCC

AGND

INN

INP

TO COMMON-MODE INPUT

2.2k

Ω

TO COMMON-MODE INPUT

2.2k

Ω

Figure 2. Simplified Analog Input Architecture

REFERENCE

BUFFER

REFIO

REFADJ

AVCC

AVCC/2

CONTROL LINE TO

DISABLE REFERENCE

BUFFER

ADC FULL-SCALE = REFT - REFB

G

1V

1k

Ω

0.1

μF

REFERENCE

SCALING

AMPLIFIER

REFT

REFB

Figure 3. Simplified Reference Architecture

相关PDF资料 |

PDF描述 |

|---|---|

| VE-25N-MX-F2 | CONVERTER MOD DC/DC 18.5V 75W |

| VE-J6R-MX-F2 | CONVERTER MOD DC/DC 7.5V 75W |

| D38999/20WE6PB | CONN RCPT 6POS WALL MNT W/PINS |

| VE-25M-MX-F4 | CONVERTER MOD DC/DC 10V 75W |

| VE-J6M-MX-F4 | CONVERTER MOD DC/DC 10V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1124EVKIT | 功能描述:数据转换 IC 开发工具 Evaluation Kit for the MAX1121 MAX1122 MAX1123 MAX1124 RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MAX1125 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125AIBH | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125AIDO | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125BIBH | 制造商:Maxim Integrated Products 功能描述:44 PIN COUNT UCSP PACKAGE TYPE - Bulk |

发布紧急采购,3分钟左右您将得到回复。