- 您现在的位置:买卖IC网 > PDF目录9827 > MAX1124EGK+TD (Maxim Integrated Products)IC ADC 10BIT PAR 250MSPS 68QFN PDF资料下载

参数资料

| 型号: | MAX1124EGK+TD |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/17页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT PAR 250MSPS 68QFN |

| 标准包装: | 2,500 |

| 位数: | 10 |

| 采样率(每秒): | 250M |

| 数据接口: | LVDS,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 657mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | * |

| 封装/外壳: | * |

| 供应商设备封装: | * |

| 包装: | * |

| 输入数目和类型: | 1 个单端,单极;1 个差分,单极 |

MAX1124

with an LVDS-compatible clock to achieve the best

dynamic performance. The clock signal source must be

a high-quality, low phase noise to avoid any degrada-

tion in the noise performance of the ADC. The clock

inputs (CLKP, CLKN) are internally biased to 1.2V,

accept a differential signal swing of 0.2VP-P to 1.0VP-P

and are usually driven in AC-coupled configuration.

See the

Differential, AC-Coupled Clock Input in the

Applications Information section for more circuit details

on how to drive CLKP and CLKN appropriately.

Although not recommended, the clock inputs also

accept a single-ended input signal.

The MAX1124 also features an internal clock manage-

ment circuit (duty-cycle equalizer) that ensures that the

clock signal applied to inputs CLKP and CLKN is

processed to provide a 50% duty cycle clock signal,

which desensitizes the performance of the converter to

variations in the duty cycle of the input clock source.

Note that the clock duty-cycle equalizer cannot be

turned off externally and requires a minimum clock fre-

quency of >20MHz to work appropriately and accord-

ing to data sheet specifications.

Clock Outputs (DCLKP, DCLKN)

The MAX1124 features a differential clock output, which

can be used to latch the digital output data with an

external latch or receiver. Additionally, the clock output

can be used to synchronize external devices (e.g.,

FPGAs) to the ADC. DCLKP and DCLKN are differential

outputs with LVDS-compatible voltage levels. There is a

2.1ns delay time between the rising (falling) edge of

CLKP (CLKN) and the rising edge of DCLKP (DCLKN).

See Figure 4 for timing details.

Divide-by-2 Clock Control (CLKDIV)

The MAX1124 offers a clock control line (CLKDIV),

which supports the reduction of clock jitter in a system.

Connect CLKDIV to OGND to enable the ADC’s internal

divide-by-2 clock divider. Data is now updated at one-

half the ADC’s input clock rate. CLKDIV has an internal

pulldown resistor and can be left open for applications

that only operate with update rates one-half of the con-

verter’s sampling rate. Connecting CLKDIV to OVCC

allows data to be updated at the speed of the ADC input

clock.

System Timing Requirements

Figure 4 depicts the relationship between the clock

input and output, analog input, sampling event, and

data output. The MAX1124 samples on the rising

(falling) edge of CLKP (CLKN). Output data is valid on

the next rising (falling) edge of the DCLKP (DCLKN)

clock, but has an internal latency of nine clock cycles.

1.8V, 10-Bit, 250Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

12

______________________________________________________________________________________

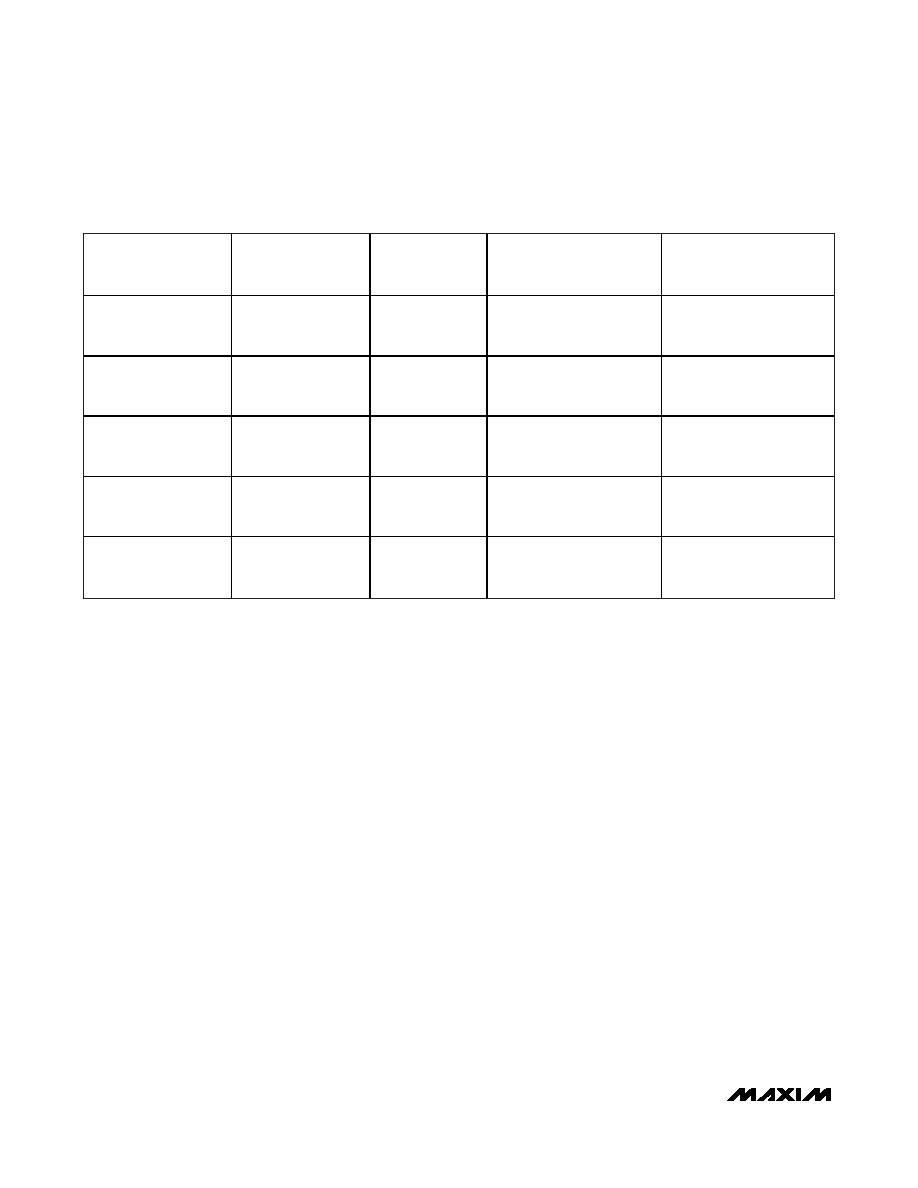

INP ANALOG

VOLTAGE LEVEL

INN ANALOG

VOLTAGE LEVEL

OUT-OF-RANGE

ORP (ORN)

BINARY

DIGITAL OUTPUT CODE

(D9–D0)

TWO’S COMPLEMENT

DIGITAL OUTPUT CODE

(D9–D0)

> VCM + 0.3125V

< VCM - 0.3125V

1 (0)

11 1111 1111

(exceeds positive full scale,

OR set)

01 1111 1111

(exceeds positive full scale,

OR set)

VCM + 0.3125V

VCM - 0.3125V

0 (1)

11 1111 1111

(represents positive full

scale)

01 1111 1111

(represents positive full

scale)

VCM

0 (1)

10 0000 0000 or

01 1111 1111

(represents midscale)

00 0000 0000 or

11 1111 1111

(represents midscale)

VCM - 0.3125V

VCM + 0.3125V

0 (1)

00 0000 0000

(represents negative full

scale)

10 0000 0000

(represents negative full

scale)

< VCM - 0.3125V

> VCM + 0.3125V

1 (0)

00 0000 0000

(exceeds negative full scale,

OR set)

10 0000 0000

(exceeds negative full scale,

OR set)

Table 1. MAX1124 Digital Output Coding

相关PDF资料 |

PDF描述 |

|---|---|

| VE-25N-MX-F2 | CONVERTER MOD DC/DC 18.5V 75W |

| VE-J6R-MX-F2 | CONVERTER MOD DC/DC 7.5V 75W |

| D38999/20WE6PB | CONN RCPT 6POS WALL MNT W/PINS |

| VE-25M-MX-F4 | CONVERTER MOD DC/DC 10V 75W |

| VE-J6M-MX-F4 | CONVERTER MOD DC/DC 10V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1124EVKIT | 功能描述:数据转换 IC 开发工具 Evaluation Kit for the MAX1121 MAX1122 MAX1123 MAX1124 RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MAX1125 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125AIBH | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125AIDO | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Bit, 300Msps Flash ADC |

| MAX1125BIBH | 制造商:Maxim Integrated Products 功能描述:44 PIN COUNT UCSP PACKAGE TYPE - Bulk |

发布紧急采购,3分钟左右您将得到回复。