参数资料

| 型号: | MAX1409CAP+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 15/48页 |

| 文件大小: | 0K |

| 描述: | IC DAS 16BIT LP 20-SSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 类型: | 数据采集系统(DAS) |

| 分辨率(位): | 16 b |

| 采样率(每秒): | 60 |

| 数据接口: | 串行 |

| 电压电源: | 模拟和数字 |

| 电源电压: | 2.7 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 20-SSOP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

MAX1407/MAX1408/MAX1409/MAX1414

Low-Power, 16-Bit Multichannel DAS with

Internal Reference,10-Bit DACs, and RTC

22

______________________________________________________________________________________

Signal Detect

The INT pin will also go low and stay low when the dif-

ferential voltage on the selected analog inputs exceeds

the signal-detect comparator trip threshold (0mV for the

MAX1407/MAX1408/MAX1409 and 50mV for the

MAX1414). This will latch the SDC bit of the Status reg-

ister to one. Additional signal detect interrupts cannot

be generated unless the SDC bit is cleared. To clear

the SDC bit, the Status register must be read and the

input must be below the signal-detect threshold.

Powering down the signal detect-comparator without

reading the Status register will also clear the SDC bit.

Similar to the power-up case, INT goes high when the

device detects a start bit through the serial interface

from the P.

Time of Day Alarm

If the device is in Sleep mode, the alarm will wake up

the device and set the ALIRQ bit. INT is asserted when

the PLL is turned on. If an alarm occurs while the

device is awake (BIASE = 1), the ALIRQ bit will be set

and INT will go low. INT remains low until the device

detects a start bit through the serial interface from the

P. ALIRQ is reset to 0 when any alarm register is read

or written to.

Shutdown (S

SH

HD

DN

N)

SHDN is an active-low output that can be used to con-

trol an external power supply. Powering up the PLL

(PLLE = 1) or writing a “1” to the SHDE bit of the

Power2 register causes SHDN to go high. SHDN goes

low when the SHDE bit is set to 0 only if the PLL is pow-

ered down (PLLE = 0). The SHDN output stays high for

2.93ms (tDPD) after receiving a power-down command,

allowing the external power supply to stay alive so that

the P can properly complete a shutdown sequence.

SHDN is not available on the MAX1409. Note: Entering

Sleep mode automatically sets PLLE and SHDE to 0.

Any wake-up event will cause SHDN to go high. (See

Wake-Up section.)

Data Ready (D

DR

RD

DY

Y)

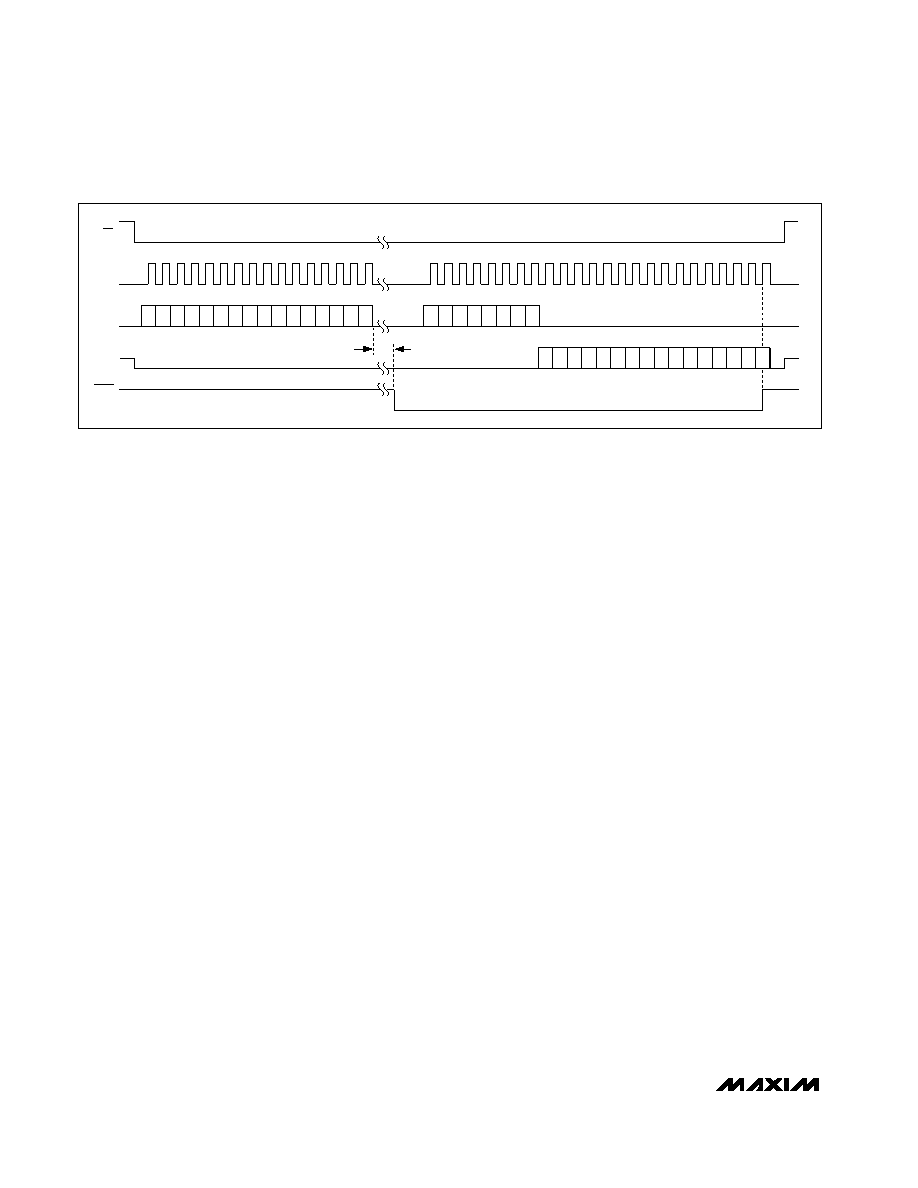

This pin will go low and stay low upon completion of an

ADC conversion or end of an ADC calibration. This sig-

nals the P that a valid conversion or calibration result

has been written to the DATA or the OFFSET register.

The DRDY pin goes high either when the P has fin-

ished reading the conversion/calibration result on the

last rising edge of SCLK (see Figure 8), or when the

next conversion result is about to be written to the

DATA register. When no read operation is performed,

DRDY pulses at 60Hz with a pulse high time of

162.76s (or 30Hz with a pulse high time of 325.52s)

DRDY is not available on the MAX1409. To see when

the ADC has completed a normal conversion or a cali-

bration conversion for the MAX1409, check the status

of the ADD bit in the Status register.

Serial Digital Interface

The SPI/QSPI/MICROWIRE-serial interface consists of

chip select (CS), serial clock (SCLK), data in (DIN), and

data out (DOUT) (See Figure 9). The serial interface

provides access to 29 on-chip registers, allowing con-

trol to all the power modes and functional blocks,

including the ADCs, DACs, and RTC. Table 2 lists the

address and read/write accessibility of all the registers.

A logic high on CS three-states DOUT and causes the

MAX1407/MAX1408/MAX1409/MAX1414 to ignore any

signals on SCLK and DIN. To clock data into or out of

the internal shift register, drive CS low. SCLK synchro-

nizes the data transfer. The rising edge of SCLK clocks

DIN into the shift register, and the falling edge of SCLK

Figure 8. ADC Conversion Timing Diagram

CS

SCLK

DIN

DOUT

1

0 A4 A3 A2 A1 A0 x

1

1 A4 A3 A2 A1 A0 x

D7 D6 D5 D4 D3 D2 D1 D0

D8

D9

D15 D14 D13 D12 D11 D10

DRDY

D7 D6 D5 D4 D3 D2 D1 D0

ADC

CONV

相关PDF资料 |

PDF描述 |

|---|---|

| V300A3V3M200BL3 | CONVERTER MOD DC/DC 3.3V 200W |

| VI-24K-MY-S | CONVERTER MOD DC/DC 40V 50W |

| V300A3V3M200BG | CONVERTER MOD DC/DC 3.3V 200W |

| VI-24J-MY-S | CONVERTER MOD DC/DC 36V 50W |

| VI-24H-MY-S | CONVERTER MOD DC/DC 52V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1409EAP | 制造商:Maxim Integrated Products 功能描述:LOW-POWER, 16-BIT MULTICHANNEL DAS WITH INTER - Bulk |

| MAX140C/D | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX140CMH | 制造商:Maxim Integrated Products 功能描述:44 PINS MQFP PKG - Bulk |

| MAX140CMH+ | 制造商:Maxim Integrated Products 功能描述:ADC SGL DUAL SLOPE 3 1/2DIGIT LED 44MQFP - Rail/Tube |

| MAX140CMH+D | 功能描述:模数转换器 - ADC 3 1/2 Dgt ADC w/Ref CPump LED Drivers RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。