- 您现在的位置:买卖IC网 > PDF目录3764 > MAX3107EAG+T (Maxim Integrated Products)IC UART SPI/I2C 128 FIFO 24SSOP PDF资料下载

参数资料

| 型号: | MAX3107EAG+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 39/52页 |

| 文件大小: | 0K |

| 描述: | IC UART SPI/I2C 128 FIFO 24SSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 特点: | 内部振荡器 |

| 通道数: | 4,QUART |

| FIFO's: | 128 字节 |

| 规程: | RS232,RS485 |

| 电源电压: | 2.35 V ~ 3.6 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 标准包装 |

| 其它名称: | MAX3107EAG+TDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

SPI/I2C UART with 128-Word FIFOs

Serial Controller Interface

The MAX3107 can be controlled through SPI or I2C as

defined by the logic on I2C/SPI. See the Pin Configurations

for further details.

SPI Interface

The SPI supports both single-cycle and burst-read/write

access. The SPI master must generate clock and data

signals in SPI MODE0 (i.e., with clock polarity CPOL = 0

and clock phase CPHA = 0).

SPI Single-Cycle Access

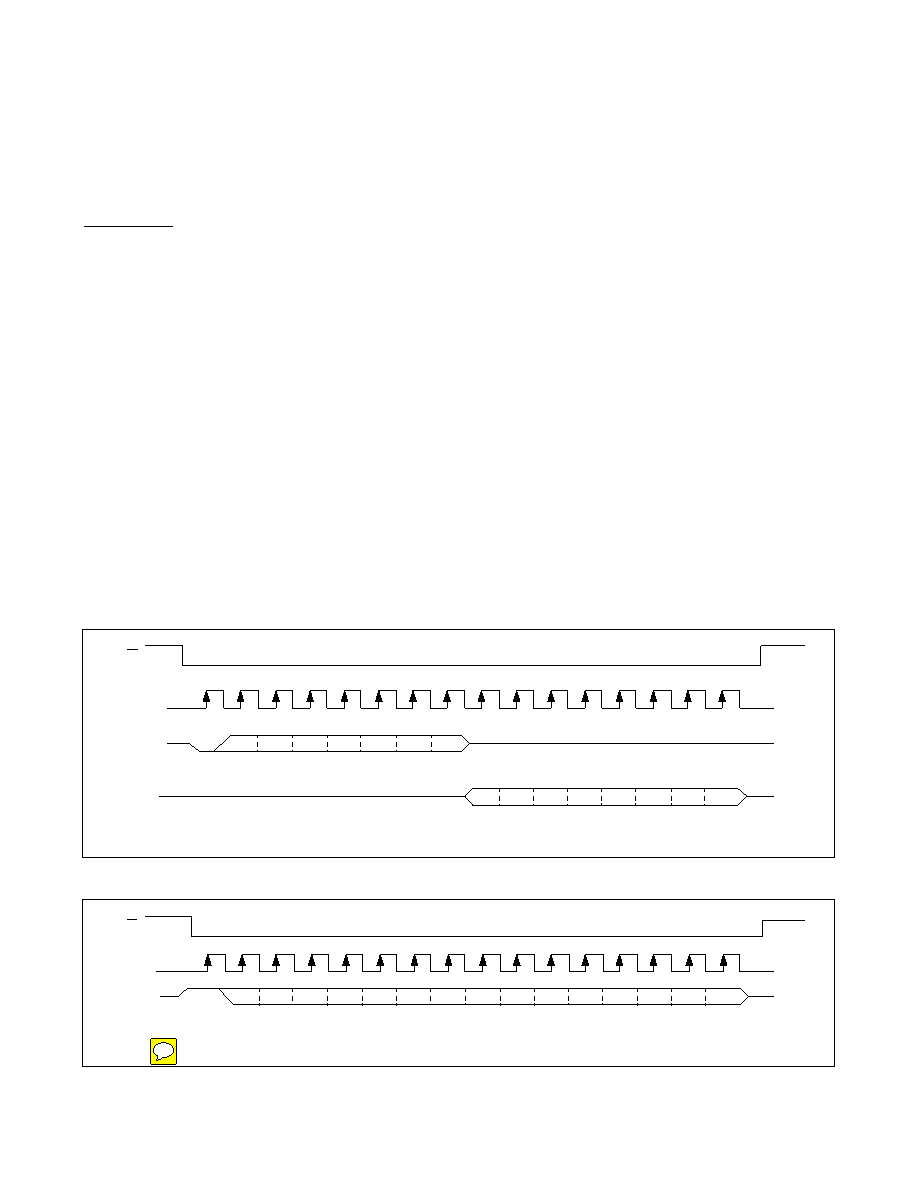

Figure 15 shows a single-cycle read and Figure 16

shows a single-cycle write.

SPI Burst Access

Burst access allows writing and reading in one block by

only defining the initial register address in the SPI com-

mand byte. Multiple characters can be loaded into the

transmit FIFO by using the THR (0x00) as the initial burst

read address. Similarly, multiple characters can be read

out of the receiver FIFO by using the RHR (0x00) as the

SPI’s burst read address. If the SPI burst address is dif-

ferent to 0x00, the MAX3107 automatically increments

the register address after each SPI data byte. Efficient

programming of multiple consecutive registers is thus

possible. Chip select, CS/A0, must be kept low during

the whole cycle. The SCLK/SCL clock continues clocking

throughout the burst access cycle. The burst cycle ends

when the SPI master pulls CS/A0 high.

For example, writing 128 bytes into the TxFIFO can be

achieved by a burst write access through the following

sequence:

Pull CS/A0 low

Send SPI write command

Send 128 byes

Release CS/A0

This takes a total of (1 + 128) x 8 clock cycles.

I2C Interface

The MAX3107 contains an I2C-compatible interface for

data communication with a host processor (SCL and

SDA). The interface supports a clock frequency up to

400kHz. SCL and SDA require pullup resistors that are

connected to a positive supply.

Figure 15. SPI Single-Cycle Read

Figure 16. SPI Single-Cycle Write

CS

R

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

SCLK

SDI

SDO

A_ = REGISTER ADDRESS

D_ = 8-BIT REGISTER CONTENTS

CS

W

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

SCLK

SDI

A_ = REGISTER ADDRESS

D_ = 8-BIT REGISTER CONTENTS

44

Maxim Integrated

MAX3107

相关PDF资料 |

PDF描述 |

|---|---|

| SC28C94A1A,518 | IC UART QUAD W/FIFO 52-PLCC |

| SC16C754BIA68,518 | IC UART QUAD W/FIFO 68-PLCC |

| SC26C92C1N,602 | IC UART DUAL W/FIFO 40-DIP |

| SC28L91A1B,551 | IC UART SINGLE W/FIFO 44-PQFP |

| SC28L91A1B,528 | IC UART SINGLE W/FIFO 44PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX3107ETG/V+ | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG/V+T | 功能描述:UART 接口集成电路 SPI/IC UART with 128-Word FIFOs and Internal Oscillator RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG+ | 功能描述:UART 接口集成电路 SPI/I2C Compatible RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG+T | 功能描述:UART 接口集成电路 SPI/I2C Compatible RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107EVKIT+ | 功能描述:UART 接口集成电路 UART with integrated Oscillator RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。